# Smart Two Channel Low-Side Switch

### Features

- Power limitation

- Overtemperature protection

- Overload protection

- Short circuit protection

- Diagnostic feedback

- Overvoltage protection

- µC compatible input

- Electrostatic discharge (ESD) protection

#### Application

- All kinds of resistive and inductive loads (relays,electromagnetic valves)

- µC compatible power switch

- Solenoid control switch in automotive and industrial control systems

### Product Summary

| Supply voltage       | Vs                     | 6.5 - 40 | V |

|----------------------|------------------------|----------|---|

| Drain source voltage | V <sub>DS(AZ)max</sub> | 60       | V |

| On resistance        | R <sub>ON (typ)</sub>  | 0.21     | Ω |

| Output current       | l <sub>D</sub>         | 2 x 4    | А |

| Nom. output current  | I <sub>D(ISO)</sub>    | 2 x 1.3  | А |

#### **General description**

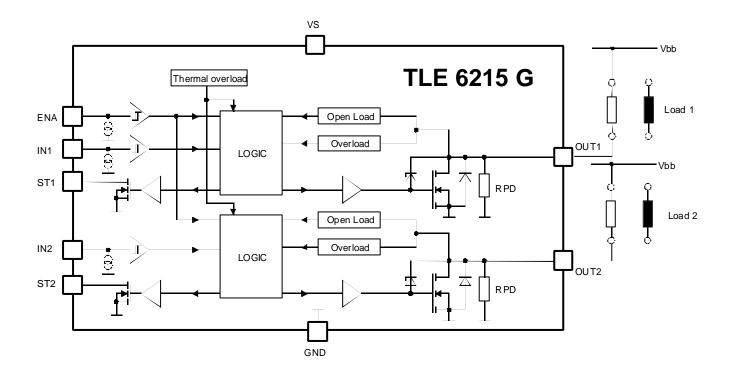

Double channel Low-Side-Switch in Smart Power Technology (SPT) with

two seperate inputs and two open drain DMOS output stages. The TLE 6215 G is fully protected by embedded protection functions and designed for automotive and industrial applications.

### **Block Diagram**

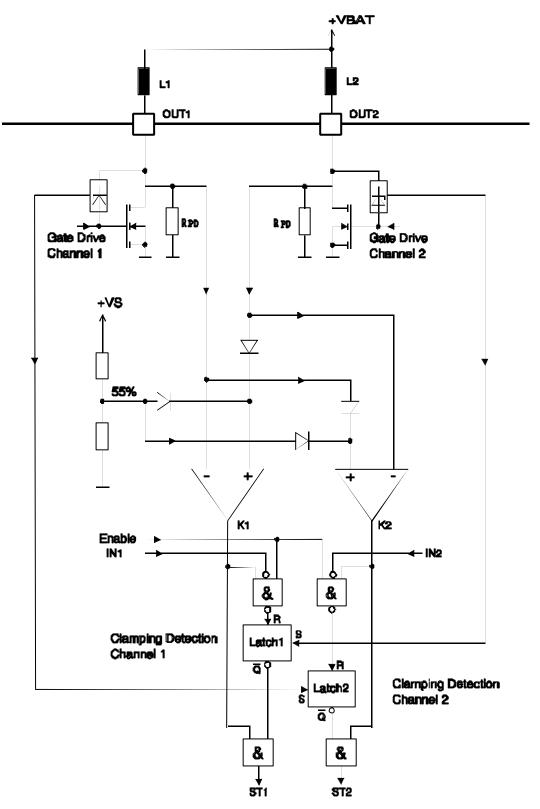

## **Block Diagram of Open Load Detection**

## Maximum Ratings for $T_j = -40^{\circ}C$ to $150^{\circ}C$

| Parameter                                                                                                                                                     | Symbol                               | Values               | Unit   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------|--------|

| Supply voltage                                                                                                                                                | Vs                                   | - 0.3 + 40           | V      |

| Supply voltage operational range                                                                                                                              | Vs                                   | + 4.8 + 40           | V      |

| Continuous drain source voltage (OUT1, OUT2)                                                                                                                  | V <sub>DS</sub>                      | 45                   | V      |

| Input voltage IN1, IN2, ENA                                                                                                                                   | V <sub>IN</sub>                      | - 0.3 + 6            | V      |

| Status output voltage                                                                                                                                         | V <sub>ST</sub>                      | - 0.3 + 32           | V      |

| Operating temperature range                                                                                                                                   | Tj                                   | - 40 + 150           | °C     |

| Storage temperature range                                                                                                                                     | $T_{ m stg}$                         | - 55 + 150           |        |

| Output current per channel                                                                                                                                    | I <sub>D(lim)</sub>                  | Overload<br>shutdown | А      |

| Output current at reversal supply                                                                                                                             | <i>I</i> <sub>D 1,2</sub>            | - 4                  | А      |

| Status output current                                                                                                                                         | I <sub>ST</sub>                      | - 5 + 5              | mA     |

| Inductive load single switch off dissipation energy $T_j = 25^{\circ}C C$                                                                                     | E <sub>AS</sub>                      | 50                   | mJ     |

| Electrostatic Discharge Voltage (HBM) according to MIL STD<br>883D, method 3015.7 and EOS/ESD assn. Standard S5.1 –<br>1993 Output 1,2 Pins<br>All other Pins | V <sub>ESD</sub><br>V <sub>ESD</sub> | 4000<br>2000         | V<br>V |

| Thermal resistance junction - case <sup>1</sup>                                                                                                               | <i>R</i> <sub>thJC</sub>             | 12                   | K/W    |

| junction - ambient                                                                                                                                            | $R_{ m thJA}$                        | 75                   |        |

| Maximum operating lifetime (according to "Ambient thermal conditions")                                                                                        | t <sub>b</sub>                       | 10000                | h      |

### Ambient thermal conditions

| Pos | T <sub>Ambient</sub> temperature ran-<br>ge | operating periods |

|-----|---------------------------------------------|-------------------|

| 11  | -40 °C                                      | 2 %               |

| 12  | -20 °C                                      | 10 %              |

| 13  | 25 °C                                       | 24 %              |

| 14  | 60 °C                                       | 34 %              |

| 15  | 80 °C                                       | 24 %              |

| 16  | 100 °C                                      | 5 %               |

| 17  | > 120 °C                                    | 1 %               |

<sup>&</sup>lt;sup>1</sup> Case = Pin 5 to 8 and 17 to 20.

Additionally the pins not connected (N.C.) have to be connected to the ground plane used as thermal heatsink to achieve the best thermal resistance.

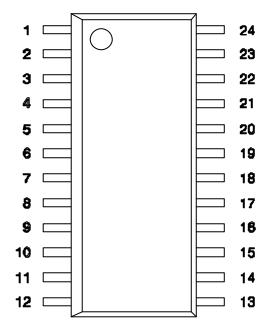

## **Pin Definitions and Functions**

| Pin         | Symbol | Function                       |

|-------------|--------|--------------------------------|

| 1           | IN1    | Control input channel 1        |

| 2           | ST2    | Status output channel 2        |

| 3           | OUT2   | Power output channel 2         |

| 4           | N.C.   | Not connected, cooling         |

| 5,6,7,8     | GND    | Ground, cooling                |

| 9,10        | N.C.   | Not connected, cooling         |

| 11          | ENA    | Enable input for both channels |

| 12          | Vs     | Supply voltage                 |

| 13,14,15,16 | N.C.   | Not connected, cooling         |

| 17,18,19,20 | GND    | Ground, cooling                |

| 21          | N.C.   | Not connected, cooling         |

| 22          | OUT1   | Power output channel 1         |

| 23          | ST1    | Status output channel 1        |

| 24          | IN2    | Control input channel 2        |

## Pin Configuration(top view)

15

30

45

μA

## **Electrical Characteristics**

| Parameter and Conditions                          |                            | Symbol                   | Values |      |      | Unit |

|---------------------------------------------------|----------------------------|--------------------------|--------|------|------|------|

| $V_S$ = 6.5 to 40 V ; $T_j$ = - 40 °C to + 150 °C |                            |                          | min    | typ  | max  |      |

| (unless otherwise specified)                      |                            |                          |        |      |      |      |

| 1. Power Supply (V <sub>s</sub> )                 |                            |                          |        |      |      |      |

| Supply current (Outputs ON)                       | $V_{S} = 40 V$             | I <sub>S</sub>           |        |      | 5    | mA   |

|                                                   | $V_S \le 18 \text{ V}$     |                          |        | 2,5  | 4    |      |

| Supply current (Output OFF)                       | $V_S \le 18 \text{ V}$     | I <sub>S</sub>           |        | 1,5  | 3    | mA   |

| Operating voltage                                 |                            | Vs                       | 4.8    |      | 40   | V    |

| 2. Power Outputs                                  |                            |                          |        |      |      |      |

| ON state resistance;                              | $T_j = 25 \circ C$         | R <sub>DS(ON)</sub>      |        | 0.21 |      | Ω    |

| $I_D = 4A; V_S \ge 9.5 V$                         | $T_j = 150^{\circ}C$       |                          |        |      | 0.42 |      |

| Z-Diode clamping voltage (OUT1, OUT2)             |                            | V <sub>DS(AZ)</sub>      | 45     |      | 60   | V    |

| Pull down resistor                                | $T_j = 25 \circ C$         | R <sub>PD</sub>          | 14     | 20   | 26   | kΩ   |

|                                                   | $T_j \le 125 \ ^\circ C$   |                          | 10     |      | 40   |      |

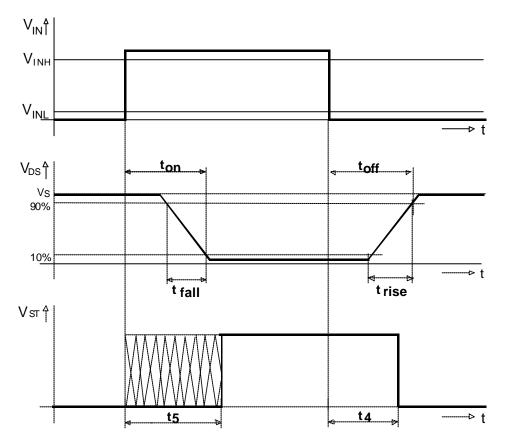

| Output on delay time <sup>2</sup>                 | $I_{D} = 0.2 \text{ A}$    | <i>t</i> on              | 10     | 25   | 40   | μs   |

| Output off delay time <sup>2</sup>                | $I_D = 2 A$                | <i>t</i> off             |        | 40   |      |      |

| Output on fall time <sup>2</sup>                  | $I_{D} = 0.2 \text{ A}$    | <i>t</i> <sub>fall</sub> |        | 20   |      |      |

| Output off rise time <sup>2</sup>                 | $I_D = 2 A$                | <i>t</i> <sub>rise</sub> |        | 25   |      |      |

| Output off status delay time <sup>2</sup>         | $I_D = 2 A$                | <i>t</i> <sub>4</sub>    | 20     | 40   | 60   |      |

| Output on status delay time <sup>2 3 4</sup>      |                            | <i>t</i> <sub>5</sub>    |        |      | 50   |      |

| Overload switch-off delay time <sup>3</sup>       |                            | t <sub>DSO</sub>         | 50     |      | 150  |      |

| 3. Digital Inputs (IN1, IN2, ENA)                 |                            |                          |        |      |      |      |

| Input low voltage                                 |                            | V <sub>INL</sub>         | - 0.3  |      | 1.0  | V    |

| Input high voltage                                |                            | V <sub>INH</sub>         | 2.0    |      | 6.0  | V    |

| Input voltage hysteresis                          |                            | V <sub>INHys</sub>       | 0.2    |      | 0.6  | V    |

| Input pull down current V <sub>IN</sub> =         | =5 V; V <sub>S</sub> ≥ 9 V | I <sub>IN</sub>          | 50     | 100  | 140  | μA   |

|                                                   |                            | 1                        |        |      |      | T    |

## 4. Digital Status Outputs (ST1, ST2), open Drain

Enable pull down current

| Output voltage low   | $I_{ST} = 2 \text{ mA}$ | V <sub>STL</sub> |  | 0.5 | V  |

|----------------------|-------------------------|------------------|--|-----|----|

| Leakage current high |                         | I <sub>STH</sub> |  | 10  | μA |

I<sub>ENA</sub>

$V_{ENA} = 5 \text{ V}; \text{ } V_{S} \ge 9 \text{ V}$

$<sup>^2</sup>$  See timing diagram, resitive load condition; V\_S  $\geq$  9 V  $^3$  This parameter will not be tested but assured by design

<sup>&</sup>lt;sup>4</sup> Time till status valid after switching on or error detection

## **Electrical Characteristics**

| Parameter and Conditions                             | Symbol | Values |     |     | Unit |

|------------------------------------------------------|--------|--------|-----|-----|------|

| $V_{S} = 6.5$ to 40 V ; $T_{j} = -40$ °C to + 150 °C |        | min    | typ | max |      |

| (unless otherwise specified)                         |        |        |     |     |      |

### 5. Diagnostic Functions

| Open load detection voltage            | $V_S \le 18 \text{ V}$      | V <sub>DS(OL)</sub>  | 0.515*V <sub>S</sub>  |     | 0.585*V <sub>S</sub>  | V  |

|----------------------------------------|-----------------------------|----------------------|-----------------------|-----|-----------------------|----|

| (Output OFF)                           | V <sub>S</sub> = 12 V       |                      | 6.2                   |     | 7.0                   |    |

| Open load compare voltage <sup>5</sup> | $18V > V_{DSC} > 0.65^*V_S$ | V <sub>DS(OL)C</sub> | V <sub>DSC</sub> -1.6 |     | V <sub>DSC</sub> -0.9 | V  |

| Open load detection current (Ou        | I <sub>D(OL)</sub>          | 100                  |                       | 500 | mA                    |    |

| Overload threshold current             | $V_S \ge 9.5 V$             | I <sub>D(lim)</sub>  | 5                     |     |                       | А  |

|                                        |                             |                      |                       |     |                       |    |

| Overtemperature shutoff thresh         | old <sup>6</sup>            | $T_{\rm th}$         | 170                   |     | 200                   | °C |

| Hysteresis                             |                             | T <sub>hys</sub>     |                       | 10  |                       | K  |

## **Application Description**

This IC is specially designed to drive inductive loads (relays, electromagnetic valves). Integrated clamp-diodes limit the output voltage peak when switching off an inductive load.

For the detection of errors there are two status outputs, which monitor the following errors by logic levels:

- thermal overload,

- open and short load to ground in active an inactive mode,

- overloading of output (also shorted load to supply) in active mode.

### **Circuit Description**

#### Input Circuits

The control and enable inputs, all active high, consist of Schmitt triggers with hysteresis. All inputs are connected with pull-down current sources. Not connected inputs are interpreted as "low".

#### **Switching Stages**

The power outputs consist of a DMOS power transistor with open drain. The output stages are shortload-protected throughout the operating range. Integrated clamp-diodes limit voltage spikes produced when inductive loads are discharged.

#### **Protective Circuit**

The outputs are protected against current overload. There is no protection against reverse polarity of the supply voltage.

<sup>&</sup>lt;sup>5</sup> V<sub>DSC</sub> is the output voltage of the other channel used for open load compare detection

<sup>&</sup>lt;sup>6</sup> This parameter will not be tested but assured by design

#### Error Detection

The status output signal of the switching stages at normal operation is LOW = OFF; HIGH = ON. In case of any error the status outputs are set according to the table below. If <u>current overload</u> or <u>thermal</u> <u>overload</u> occurs, the error condition is stored in an internal register and the output is shutdown. To reset this register the control input of the affected channel has to be switched off and then on again. The state of the error detection circuit is directly dependent on the input status. Open load is detected for both on- and off-modus.

In the on-modus the load current is monitored. If it drops below the specified threshold open load is detected. In the off mode, the ouput voltage is monitored.

An open load condition is detected when the output voltage of a given channel is below 55 % of the supply voltage Vs. Also the output voltages of two outputs are compaired against each other in off condition with a fixed offset of typ. 1.25 V to recognize GND bypasses. To suppress fault diagnosis during the flyback phase of the compared output, the diagnostic circuit includes a latch function. Reset of this latch is done at end of the flyback phase, additionally it can be reseted by a low signal on the enable input and by a high signal of the input signal. See also the block diagramm of open load detection.

| Operating Condition       |     | Inputs |     | Power | Outputs | Status | Outputs |

|---------------------------|-----|--------|-----|-------|---------|--------|---------|

|                           | ENA | IN1    | IN2 | OUT1  | OUT2    | ST1    | ST2     |

|                           | L   | Х      | Х   | OFF   | OFF     | L      | L       |

|                           | Н   | L      | L   | OFF   | OFF     | L      | L       |

| Normal Function           | Н   | Н      | L   | ON    | OFF     | Н      | L       |

|                           | Н   | L      | Н   | OFF   | ON      | L      | Н       |

|                           | Н   | Н      | Н   | ON    | ON      | Н      | Н       |

|                           | Х   | L      | L   | OFF   | OFF     | L      | L       |

| Thermal Overload          | L   | Х      | Х   | OFF   | OFF     | L      | L       |

|                           | Н   | Н      | Н   | OFF   | OFF     | L      | L       |

|                           | Х   | L      |     | OFF   |         | Н      |         |

| Open Load Channel 1       | L   | Н      | 1)  | OFF   | 1)      | Н      | 1)      |

|                           | Н   | Н      |     | ON    |         | L      |         |

|                           | Х   |        | L   |       | OFF     |        | Н       |

| Open Load Channel 2       | L   | 1)     | Н   | 1)    | OFF     | 1)     | Н       |

|                           | Н   |        | Н   |       | ON      |        | L       |

|                           | L   | Х      |     | OFF   |         | L      |         |

| <b>Overload Channel 1</b> | Н   | L      | 1)  | OFF   | 1)      | L      | 1)      |

|                           | Н   | Н      |     | OFF   |         | L      |         |

|                           | L   |        | Х   |       | OFF     |        | L       |

| <b>Overload Channel 2</b> | Н   | 1)     | L   | 1)    | OFF     | 1)     | L       |

|                           | Н   |        | Н   |       | OFF     |        | L       |

## **Diagnostic Table**

1) see normal function

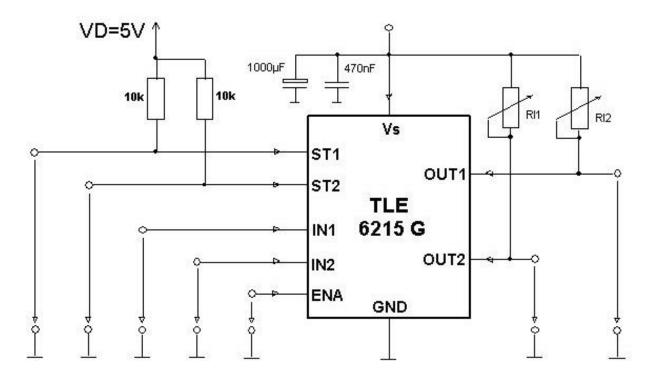

# Test Circuit

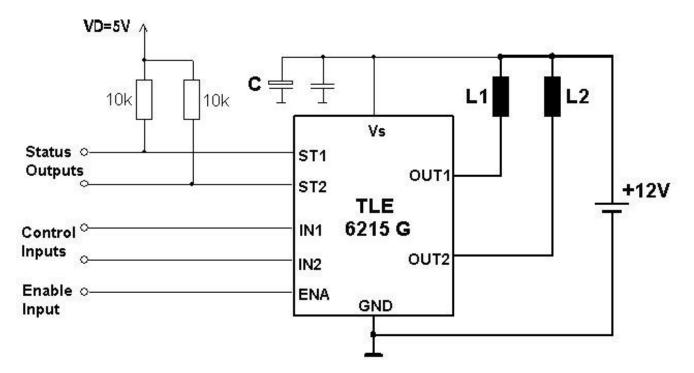

# Application Circuit

The blocking capacitor C is recommended to avoid critical negative voltage spikes on  $V_{\!s}$  in case of battery interruption during OFF-commutation.

# Timing Diagram

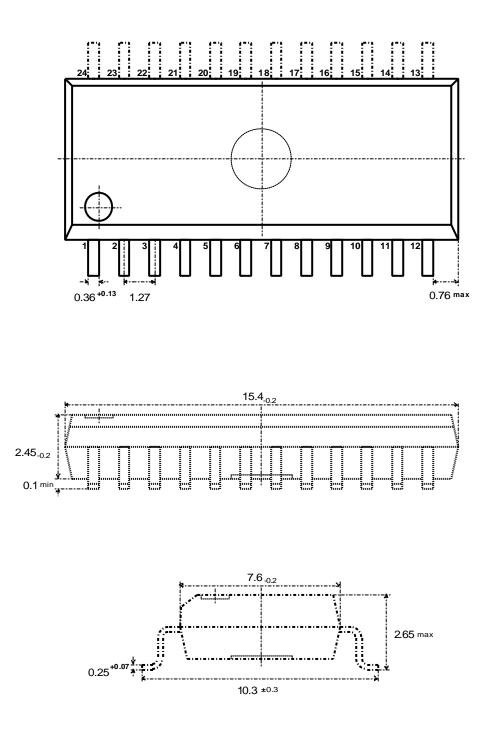

# Package and ordering code

### all dimensions in mm

| P - DSO - 24 - L16 | Ordering code |

|--------------------|---------------|

|                    |               |

(Dual-in-line package, small-outline) 24 B 24 DIN 41870 T17

Published by Infineon Technologies AG, Bereichs Kommunikation St.-Martin-Strasse 76, D-81541 München © Infineon Technologies AG 1999 All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that lifesupport device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.