# Nuvoton Bus Termination Regulator W83310G-R2

# **Data Sheet Revision History**

| NO | PAGES | DATES      | VERSION | VERSION<br>ON WEB | MAIN CONTENTS                                                                                             |

|----|-------|------------|---------|-------------------|-----------------------------------------------------------------------------------------------------------|

| 1. | All   | June, 2007 | 1.0     | N.A               | Remove non Pb-free part no: W83310S-R2                                                                    |

| 2  | All   | Nov., 2008 | 1.1     | N.A               | 1. Change to Nuvoton document format 2. Add performance chart with VIN=1.5V/1.8V/2.5V at VCNTL = 3.0~3.6V |

| 3  |       |            |         |                   |                                                                                                           |

| 4  |       |            |         |                   |                                                                                                           |

| 5  |       |            |         |                   |                                                                                                           |

| 6  |       |            |         |                   |                                                                                                           |

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

# Table of Content-

| 1.  | GENERAL DESCRIPTION               | 1    |

|-----|-----------------------------------|------|

| 2.  | FEATURES                          | 1    |

| 3.  | APPLICATIONS                      | 1    |

| 4.  | PIN CONFIGURATION AND DESCRIPTION | 2    |

| 5.  | APPLICATION CIRCUIT               | 3    |

| 6.  | INTERNAL BLOCK DIAGRAM            | 3    |

| 7.  | ABSOLUTE MAXIMUM RATINGS          | 4    |

| 8.  | RECOMMENDED OPERATING CONDITIONS  | 4    |

| 9.  | ELECTRICAL CHARACTERISTICS        | 5    |

| 10. | TYPICAL OPERATING WAVEFORMS       | 5    |

| 11. | PACKAGE DIMENSION                 | . 10 |

| 12. | ORDERING INFORMATION              | 11   |

| 13  | TOP MARKING SPECIFICATION         | 11   |

## 1. GENERAL DESCRIPTION

The W83310G-R2 is a linear regulator provides power with the capability of continuous 1.8Amp bi-directional sinking and driving capability for a high speed bus terminator application. The chip simply implements a stable power supply which tracks dynamically half of the input power for the bus terminator. The W83310G-R2 is promoted with small footprint 8-SOP 150mil package. The design of the W83310G-R2 provides a high integration, high performance, and cost-effective solution.

#### 2. FEATURES

- Support DDRI (1.25VTT), DDRII (0.9VTT) and DDRIII (0.75VTT) Requirements

- Sink and Source 1.8A Continuous Current

- Integrated Power MOSFET

- Adjustable VOUT by External Resistors

- Low External Component Count

- Low Output Voltage Offset

- Short Circuit Protection

- 0°C to 70°C Ambient Operating Temperature Range

- SOP-8 Package, Lead (Pb) Free

#### 3. APPLICATIONS

- Desktop PCs, Notebooks, and Workstations

- Graphics Card Memory Termination

- DDRI, DDRII and DDRIII Memory Systems

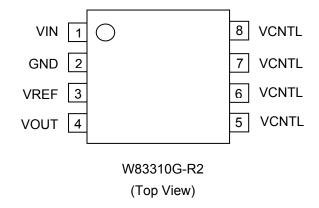

# 4. PIN CONFIGURATION AND DESCRIPTION

| SYMBOL | PIN        | I/O | FUNCTION                                                          |  |  |                                    |

|--------|------------|-----|-------------------------------------------------------------------|--|--|------------------------------------|

| VIN    | 1          | I   | Main power input pin which supplies current to the output pin.    |  |  |                                    |

| VDEE   | 7055       |     | F.F. 0 1                                                          |  |  | Internal reference voltage source. |

| VREF 3 |            | ı   | Reference voltage on the pin will be referred with the pin value. |  |  |                                    |

| VOUT   | 4          | 0   | Voltage output pin which is regulated to the VREF voltage.        |  |  |                                    |

| VCNTL  | 5, 6, 7, 8 | I   | Power for internal control logic circuitry.                       |  |  |                                    |

| GND    | 2          |     | Ground.                                                           |  |  |                                    |

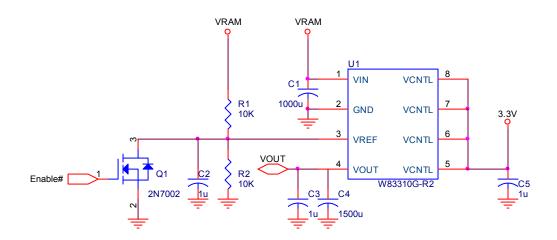

# 5. APPLICATION CIRCUIT

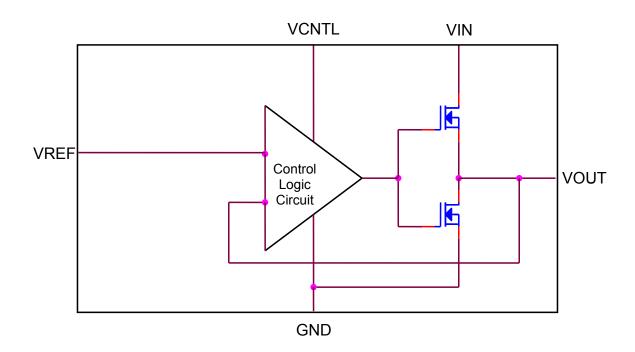

## 6. INTERNAL BLOCK DIAGRAM

## 7. ABSOLUTE MAXIMUM RATINGS

| ITEM                               | SYMBOL          | RATING     | UNIT |

|------------------------------------|-----------------|------------|------|

| Input Voltage                      | VIN             | -0.3 to 5  | V    |

| Control Logic Input Voltage        | VCNTL           | -0.3 to 5  | V    |

|                                    | Human Body Mode | ±2         | kV   |

| Electrostatic discharge protection | Machine Mode    | ±200       | V    |

|                                    | Latch-Up        | ±100       | mA   |

| Package Thermal Resistance         | $\theta_{JA}$   | 160        | °C/W |

| Storage Temperature Range          |                 | -65 to 150 | °C   |

Note: Stress listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum ration conditions for extended periods may remain possibility to affect device reliability.

## 8. RECOMMENDED OPERATING CONDITIONS

| ITEM                        | SYMBOL | MIN | MAX | UNIT |

|-----------------------------|--------|-----|-----|------|

| Input Voltage               | VIN    | 1.5 | 3.6 | V    |

| Input Voltage               | VCNTL  | 3   | 3.6 | V    |

| Operating Temperature Range |        | 0   | 70  | °C   |

| Junction Temperature Range  |        | 0   | 125 | °C   |

## 9. ELECTRICAL CHARACTERISTICS

$T_A = 25$ °C, VCNTL= 3.3 V, VIN=2.5V/1.8V/1.5V, VREF=1.25V/0.9V/0.75V,  $C_{OUT}$ =1000uF, all voltage outputs unloaded (unless otherwise noted)

| PARAMETER                            | TEST CONDITION                 | MIN                               | TYP | MAX | UNITS |    |  |

|--------------------------------------|--------------------------------|-----------------------------------|-----|-----|-------|----|--|

| Input                                |                                |                                   |     |     |       |    |  |

| VCNTL Operating Current              | I <sub>CNTL</sub>              | I <sub>OUT</sub> =0A              |     | 0.5 | 1     | mA |  |

| Shutdown Current (note 1)            | I <sub>VIN</sub> (SHDN)        | VREF<0.2V, I <sub>OUT</sub> =0.1A |     | 1   | 10    | uA |  |

| Gridita Wil Guillerit (note 1)       | I <sub>VCNTL</sub> (SHDN)      |                                   |     | 230 | 300   | uA |  |

| Output (DDRI / DDRII / DDRIII)       | Output (DDRI / DDRII / DDRIII) |                                   |     |     |       |    |  |

| Output Offset Voltage (note 2)       | Vos                            | I <sub>OUT</sub> =0A              | -5  | 0   | 5     | mV |  |

| Load Regulation (note 3)             | $\Delta V_1$                   | $I_{OUT}$ =0 $\rightarrow$ +1.8A  | -40 |     | 40    | mV |  |

| Load Negalation (note 3)             | $\Delta V_{L}$                 | I <sub>OUT</sub> =-0 → -1.8A      | -40 |     | 40    |    |  |

| Protection                           |                                |                                   |     |     |       |    |  |

| Short Current Limit I <sub>LIM</sub> |                                | V <sub>OUT</sub> short to ground  |     | 4   |       | Α  |  |

| VREF Shutdown Mode                   |                                |                                   |     |     |       |    |  |

| Shutdown Threshold                   | V <sub>IH</sub>                | Enable                            | 0.4 |     |       | V  |  |

| Shutuown miesholu                    | V <sub>IL</sub>                | Disable                           |     |     | 0.2   | V  |  |

Note 1: Shutdown current is the input current of VIN & VCNTL drawn by a regulator when the output voltage is disabled by a shutdown signal on VREF pin ( $V_{IL}$  < 0.2). It is measured with VIN = 1.5V/1.8V/2.5V & VCNTL = 3.3V.

Note 2:  $V_{OS}$  offset is the voltage measurement as  $V_{OUT}$  subtracted from VREF.

Note 3: Regulation is measured at constant junction temperature by using a 5ms current pulse. Devices are tested for load regulation in the load range from 0A to 1.8A peak.

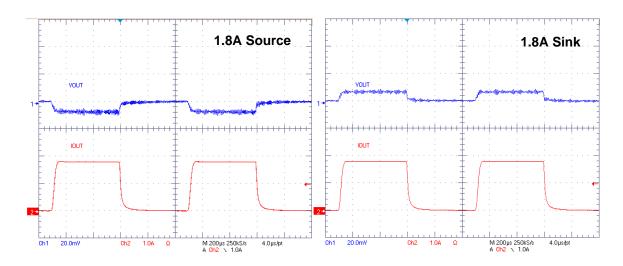

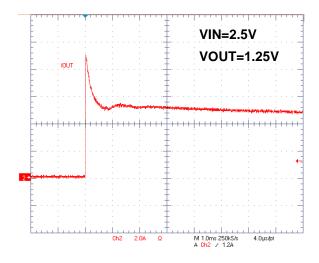

## 10. TYPICAL OPERATING WAVEFORMS

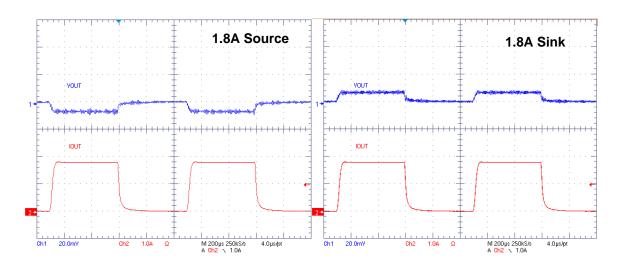

● Transient Response, VCNTL=3.3V, VIN=2.5V, VREF=1.25V, VOUT=1.25V

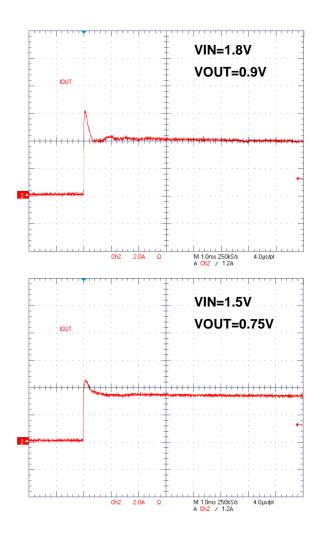

■ Transient Response, VCNTL=3.3V, VIN=1.8V, VREF=0.9V, VOUT=0.9V

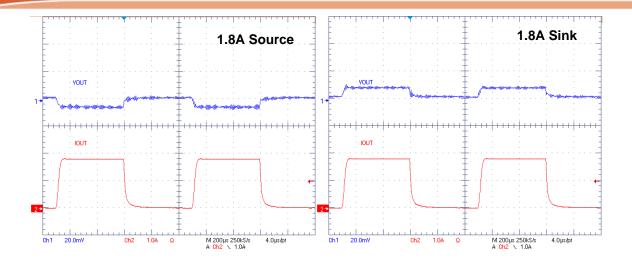

● Transient Response, VCNTL=3.3V, VIN=1.5V, VREF=0.75V, VOUT=0.75V

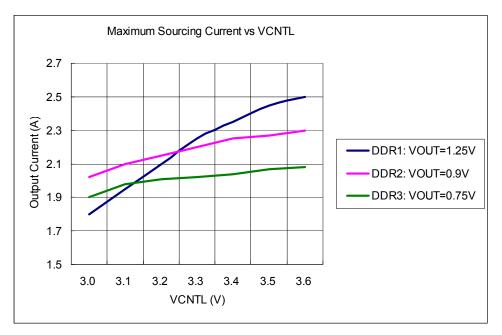

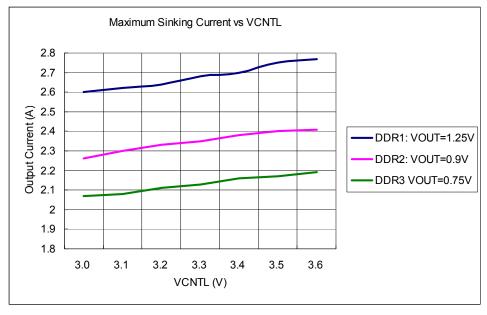

Maximum Sourcing Current with VCNTL = 3.0V ~ 3.6V

#### Note:

- ➤ DDR1: VIN = 2.5V, VOUT = 1.25V with 10ms current pulse.

- ➤ DDR2: VIN = 1.8V, VOUT = 0.9V with 10ms current pulse.

- DDR3: VIN = 1.5V, VOUT = 0.75V with 10ms current pulse.

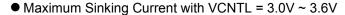

#### Note:

- DDR1: VIN = 2.5V, VOUT = 1.25V with 10ms current pulse.

- > DDR2: VIN = 1.8V, VOUT = 0.9V with 10ms current pulse.

- DDR3: VIN = 1.5V, VOUT = 0.75V with 10ms current pulse.

- Output Short Circuit Protection, VCNTL=3.3V, VOUT shorted to ground

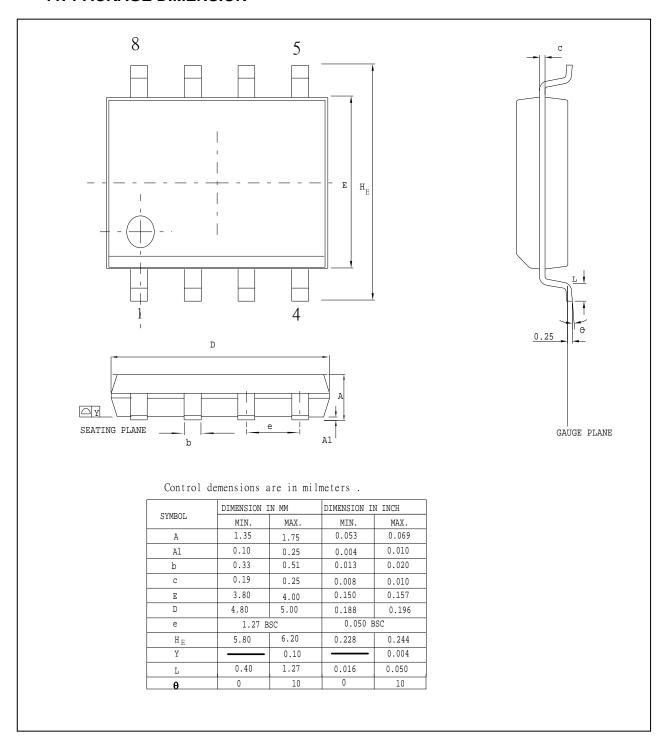

# 11. PACKAGE DIMENSION

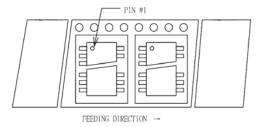

#### > TAPING SPECIFICATION

8 Pin SOP Package

## 12. ORDERING INFORMATION

| PART NUMBER | UMBER PACKAGE TYPE SUPPLIED AS |                                                     | PRODUCTION FLOW           |  |

|-------------|--------------------------------|-----------------------------------------------------|---------------------------|--|

| W83310G-R2  | 8PIN SOP(Pb-free package)      | E Shape: 100 units/Tube<br>T Shape: 2,500 units/T&R | Commercial, 0°C to +70 °C |  |

## 13. TOP MARKING SPECIFICATION

Left line: Winbond logo (Nuvoton)

1<sup>st</sup> & 2<sup>nd</sup> line: W83310G-R2 – the part number

3<sup>rd</sup> line: Tracking code <u>706 X Y</u>

706: Packages assembled in Year 07', week 06

X: Assembly house ID Code

$\underline{\mathbf{Y}}$ : The IC version Code

## **Important Notice**

Nuvoton products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further more, Nuvoton products are not intended for applications wherein failure of Nuvoton products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.