# Airbag System Basis Chip (SBC) with Power Supply and PSI5 Sensor Interface

The 33789, a SafeAssure SMARTMOS solution, is a mixed signal IC for airbag safety applications. The 33789 provides a cost effective and flexible system IC solution across the range of airbag partitions used in cars and other vehicles.

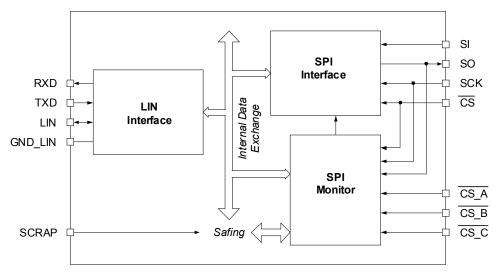

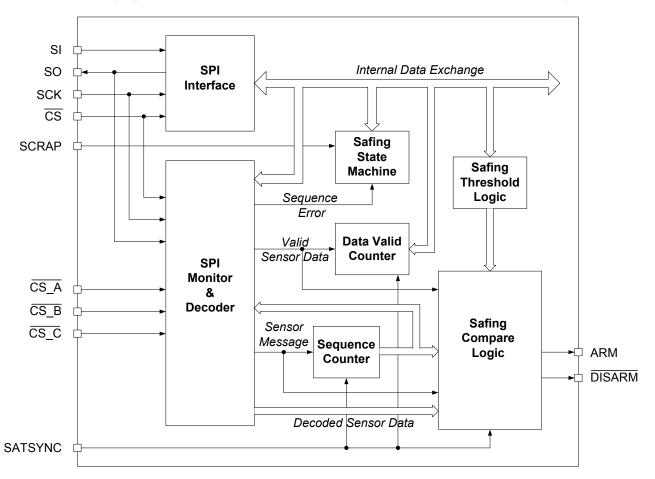

The 33789 connects to the 12 V vehicle battery and supplies the multiple voltages of a typical airbag system. The 33789 can detect switched input states, communicate with both local and remote crash sensors. It offers an industry standard interface (SPI) and four PSI5 master interfaces. The 33789 has a dedicated safing state machine that complements the airbag's MCU hardware/ software safing approach. Also included are a diagnostic - self protection capability and a programmable analog interface accessible by the system MCU.

The 33789 is well suited for use in low to high end airbag systems by allowing the designer to scale a design for the number of firing loops needed while providing enhanced safety and system reliability.

#### **Features**

- Designed to operate 5.2 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, up to a 40 V transient

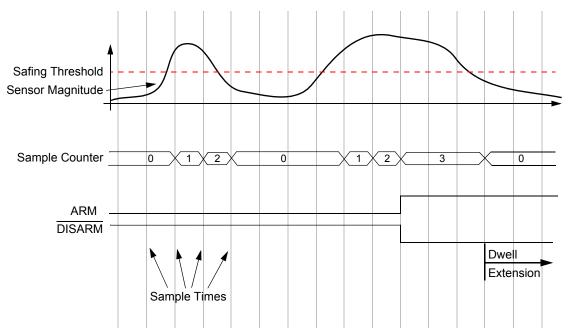

- · Safing state machine with programmable sensing thresholds

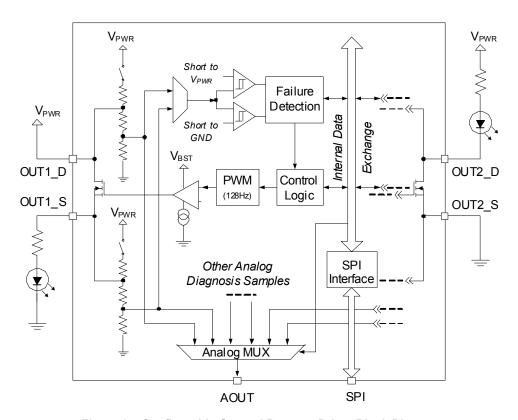

- · Two configurable high-side/low-side drivers with PWM capability

- · Four PSI5 satellite sensor master interfaces

- · Self-protected and diagnostic capability

- Watchdog and system Power ON Reset (POR)

- Supports complete airbag system power supply architecture, including system power mode control, supplies for squib firing (33 V), satellite sensors (6.3 V), and local ECU sensors and ECU logic circuits (5.0 V)

- Nine configurable switch input monitors for simple switch and Hall- effect sensor interfaces with internal power supply

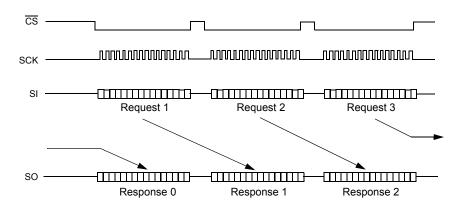

- 16-bit SPI interface

- LIN 2.1 physical layer interface

# 33789

#### **AUTO RESTRAINT**

#### **Applications**

· Airbag safety

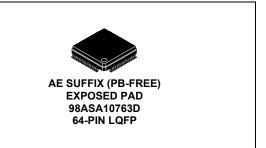

Figure 1. 33789 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

# **ORDERABLE PARTS**

This section describes the part numbers available to be purchased along with their differences. Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <a href="http://www.freescale.com">http://www.freescale.com</a> and perform a part number search for the following device numbers.

**Table 1. Orderable Part Variations**

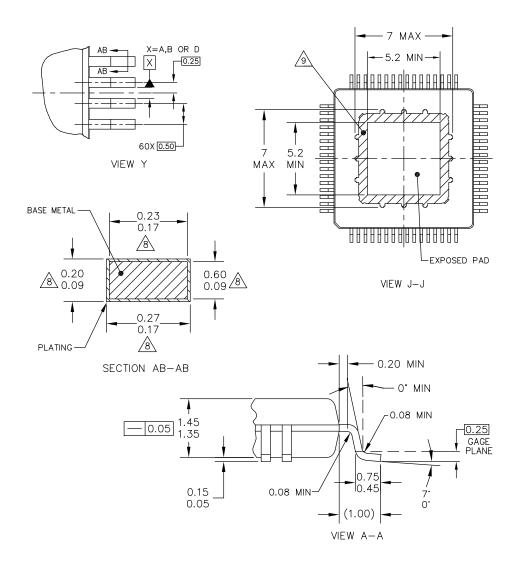

| Part Number | Notes | Temperature (T <sub>A</sub> ) | Package    |

|-------------|-------|-------------------------------|------------|

| MCZ33789BAE | (1)   | -40 °C to 125 °C              | 64 LQFP EP |

#### Notes

1. To order parts in Tape & Reel, add the R2 suffix to the part number.

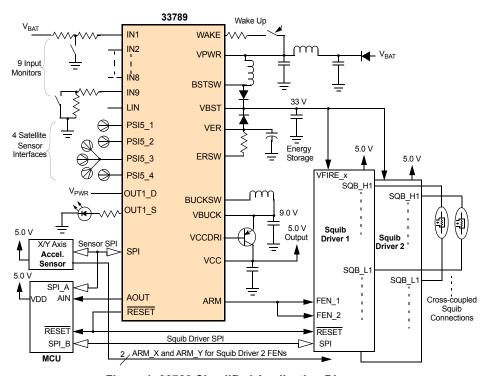

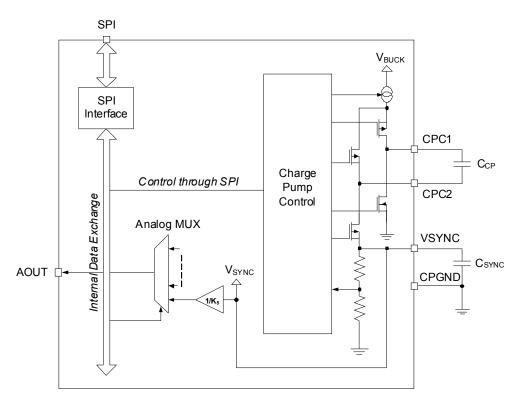

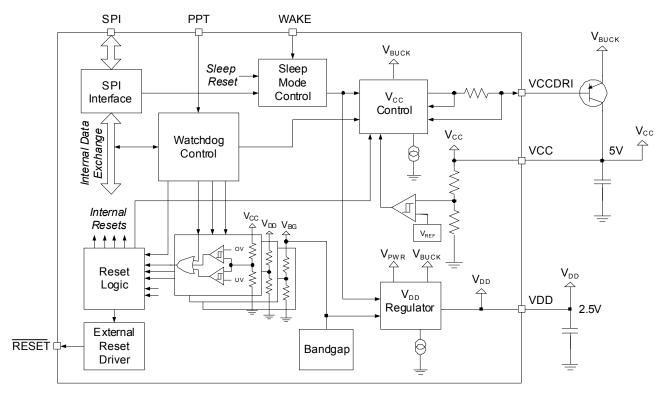

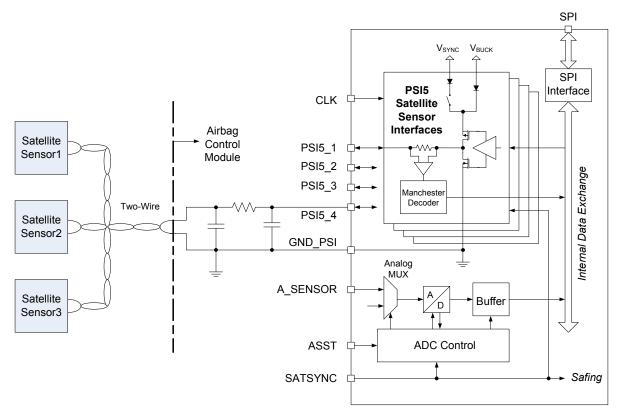

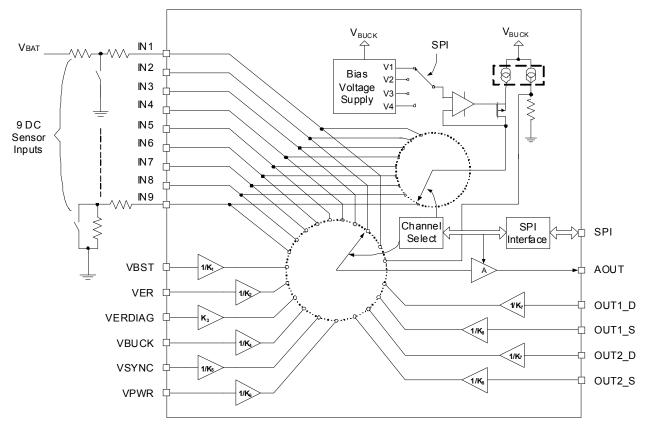

# INTERNAL BLOCK DIAGRAM

Figure 2. 33789 Simplified Internal Block Diagram

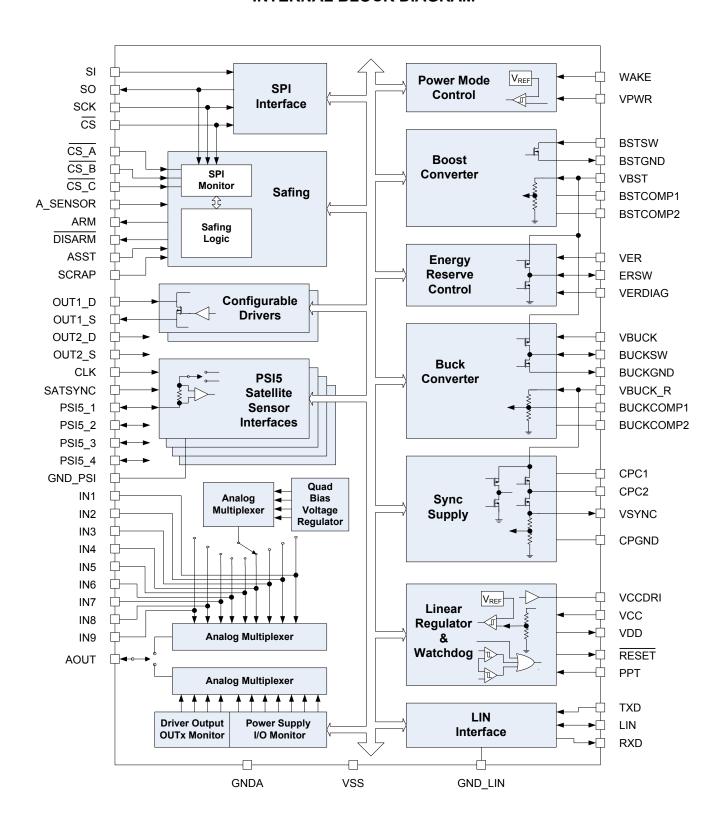

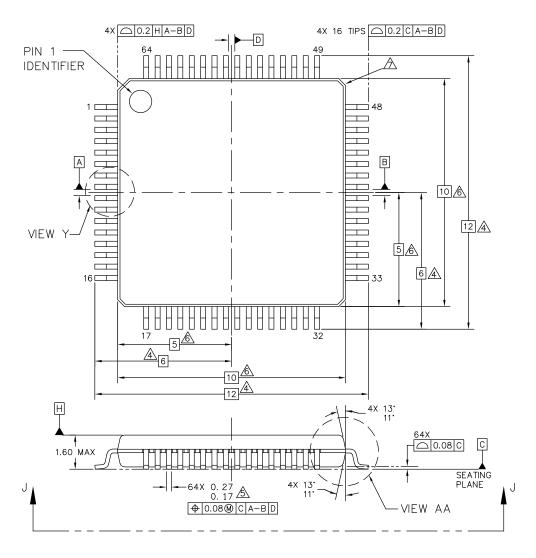

# PIN CONNECTIONS

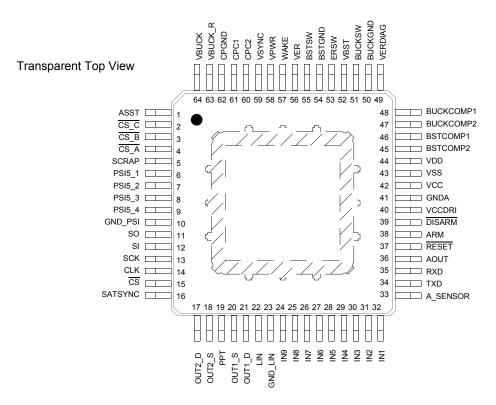

Figure 3. 33789 Pin Connections

A functional description of each pin can be found in the Functional Pin Description section beginning on page 26.

Table 2. 33789 Pin Definitions

| Din    | Pin Pin  |              |                         |                                                                                            |  |  |  |  |

|--------|----------|--------------|-------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| Number | Pin Name | Function     | Formal Name             | Definition                                                                                 |  |  |  |  |

| 1      | ASST     | Input        | Analog Sensor Self-test | Active high input to initiate analog sensor self-test                                      |  |  |  |  |

| 2      | CS_C     | Input        | Chip Select C           | Active low SPI monitor chip select input dedicated for on-board sensor C.                  |  |  |  |  |

| 3      | CS_B     | Input        | Chip Select B           | Active low SPI monitor chip select input dedicated for on-board sensor B                   |  |  |  |  |

| 4      | CS_A     | Input        | Chip Select A           | Active low SPI monitor chip select input dedicated for on-board sensor A                   |  |  |  |  |

| 5      | SCRAP    | Input        | Scrap                   | Scrap command input                                                                        |  |  |  |  |

| 6      | PSI5_1   | Input/Output | PSI5 Interface 1        | PSI5 standard interface 1 as satellite sensor channel 1                                    |  |  |  |  |

| 7      | PSI5_2   | Input/Output | PSI5 Interface 2        | PSI5 standard interface 2 as satellite sensor channel 2                                    |  |  |  |  |

| 8      | PSI5_3   | Input/Output | PSI5 Interface 3        | PSI5 standard interface 3 as satellite sensor channel 3                                    |  |  |  |  |

| 9      | PSI5_4   | Input/Output | PSI5 Interface 4        | PSI5 standard interface 4 as satellite sensor channel 4                                    |  |  |  |  |

| 10     | GND_PSI  | Ground       | PSI Ground              | Dedicated ground point for PSI5 sensor                                                     |  |  |  |  |

| 11     | SO       | Output       | SPI Data Out            | SPI data output                                                                            |  |  |  |  |

| 12     | SI       | Input        | SPI Data In             | SPI data input                                                                             |  |  |  |  |

| 13     | SCK      | Input        | SPI Clock               | SPI clock input                                                                            |  |  |  |  |

| 14     | CLK      | Input        | Satellite Sensor Clock  | Clock input for the PSI5 sensor interface(s) running in synchronous operation mode         |  |  |  |  |

| 15     | CS       | Input        | SPI Chip Select         | Active low SPI chip select input from MCU, also used for satellite channels on SPI monitor |  |  |  |  |

Table 2. 33789 Pin Definitions (continued)

| Pin<br>Number | Pin Name      | Pin<br>Function | Formal Name                                | Definition                                                                                                                |

|---------------|---------------|-----------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 16            | SATSYNC       | Input           | Satellite Sync-pulse<br>Trigger            | Satsync command input from MCU to trigger PSI5 Sync-pulse                                                                 |

| 17            | OUT2_D        | Output          | Output Driver2 Drain                       | Drain pin of the configurable driver2 outputs                                                                             |

| 18            | OUT2_S        | Output          | Output Driver2 Source                      | Source pin of the configurable driver2 outputs                                                                            |

| 19            | PPT           | Input           | Production Programming and Testing         | Active high input to enable test-mode for production programming and testing. Not for application                         |

| 20            | OUT1_S        | Output          | Output Driver1 Source                      | Source pin of the configurable driver1 outputs                                                                            |

| 21            | OUT1_D        | Output          | Output Driver1 Drain                       | Drain pin of the configurable driver1 outputs                                                                             |

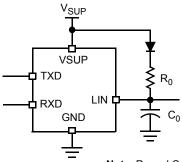

| 22            | LIN           | Input/output    | LIN Interface                              | LIN interface. It can be configured as a bi-directional pin which represents the single-wire bus transmitter and receiver |

| 23            | GND_LIN       | Ground          | LIN Ground                                 | Dedicated ground point for a bi-directional pin which represents the single-wire bus transmitter and receiver             |

| 24            | IN9           | Input           | Input Monitor Port 9                       | Port 9 of input monitor for DC sensor                                                                                     |

| 25            | IN8           | Input           | Input Monitor Port 8                       | Port 8 of input monitor for DC sensor                                                                                     |

| 26            | IN7           | Input           | Input Monitor Port 7                       | Port 7 of input monitor for DC sensor                                                                                     |

| 27            | IN6           | Input           | Input Monitor Port 6                       | Port 6 of input monitor for DC sensor                                                                                     |

| 28            | IN5           | Input           | Input Monitor Port 5                       | Port 5 of input monitor for DC sensor                                                                                     |

| 29            | IN4           | Input           | Input Monitor Port 4                       | Port 4 of input monitor for DC sensor                                                                                     |

| 30            | IN3           | Input           | Input Monitor Port 3                       | Port 3 of input monitor for DC sensor                                                                                     |

| 31            | IN2           | Input           | Input Monitor Port 2                       | Port 2 of input monitor for DC sensor                                                                                     |

| 32            | IN1           | Input           | Input Monitor Port 1                       | Port 1 of input monitor for DC sensor                                                                                     |

| 33            | A_SENSOR      | Input           | Analog Sensor Input                        | Analog sensor input for safing                                                                                            |

| 34            | TXD           | Input           | Data Input from UART                       | Logic-level data input from MCU UART transmitter for LIN/K-line                                                           |

| 35            | RXD           | Output          | Data Output to UART                        | Logic-level data output to MCU UART receiver for LIN/K-line                                                               |

| 36            | AOUT          | Output          | Analog Output                              | Analog output to send MCU scaled, multiplexed and buffered analog signals for diagnosis                                   |

| 37            | RESET         | Output          | Reset                                      | Active low reset output                                                                                                   |

| 38            | ARM           | Output          | Arm Enable                                 | Active high safing enable signal to squib driver                                                                          |

| 39            | DISARM        | Output          | Arm Disable                                | Active low safing enable signal to squib driver                                                                           |

| 40            | VCCDRI        | Output          | V <sub>CC</sub> Bypass Transistor<br>Drive | Linear regulator drive output to control an external PNP transistor for 5.0 V V <sub>CC</sub> output                      |

| 41            | GNDA          | Ground          | Analog Ground                              | Analog ground                                                                                                             |

| 42            | VCC           | Input           | V <sub>CC</sub> Input                      | 5.0 V V <sub>CC</sub> input for monitoring and internal supply                                                            |

| 43            | VSS           | Ground          | Digital Ground                             | Digital ground                                                                                                            |

| 44            | VDD           | Output          | Digital Power Supply<br>Output             | 2.5 V linear regulator output for output capacitor connection.                                                            |

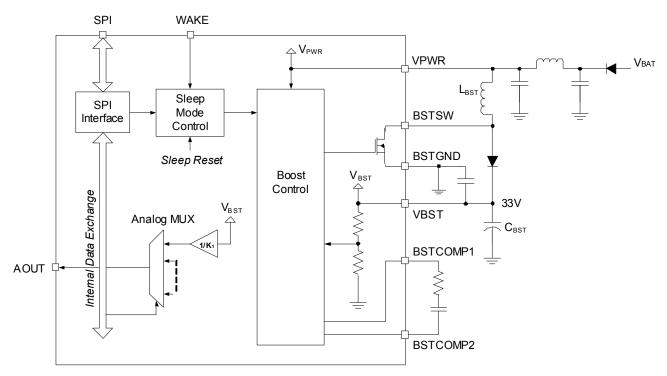

| 45            | BSTCOMP2      | Input           | Boost Compensation pin2                    | Connection 2 to the boost converter compensation network                                                                  |

| 46            | BSTCOMP1      | Input           | Boost Compensation pin1                    | Connection 1 to the boost converter compensation network                                                                  |

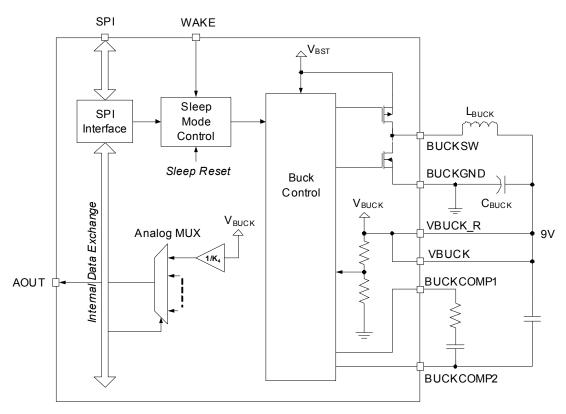

| 47            | BUCKCOM<br>P2 | Input           | Buck Compensation pin2                     | Connection 2 to the buck converter compensation network                                                                   |

| 48            | BUCKCOM<br>P1 | Input           | Buck Compensation pin1                     | Connection 1 to the buck converter compensation network                                                                   |

# Table 2. 33789 Pin Definitions (continued)

| Pin<br>Number | Pin Name | Pin<br>Function | Formal Name                       | Definition                                                                                             |

|---------------|----------|-----------------|-----------------------------------|--------------------------------------------------------------------------------------------------------|

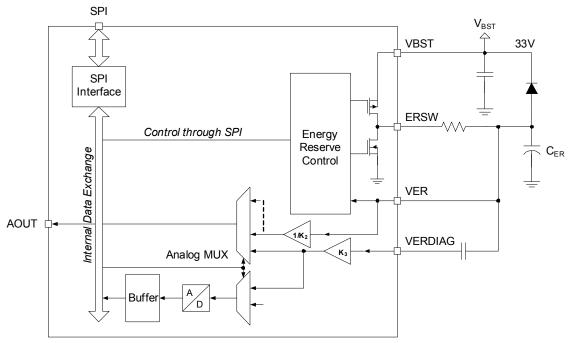

| 49            | VERDIAG  | Input           | Energy Reserve<br>Diagnosis       | AC coupled energy reserve diagnostic input                                                             |

| 50            | BUCKGND  | Ground          | Buck Converter Ground             | Ground return of the buck converter, buck switch ground                                                |

| 51            | BUCKSW   | Output          | Buck Switch                       | Buck switch driver output to connect buck inductor                                                     |

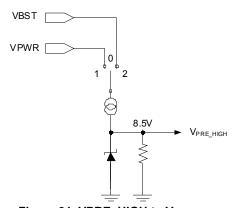

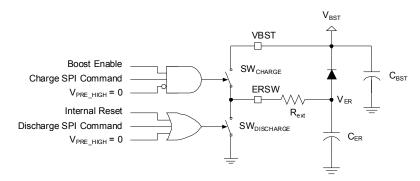

| 52            | VBST     | Input           | Boost Voltage Input               | Boost voltage input for boost loop feedback and source of buck converter, same voltage as boost output |

| 53            | ERSW     | Output          | Energy Reserve Switch             | Storage driver output to control the energy reserve capacitor charging                                 |

| 54            | BSTGND   | Ground          | Boost Converter Ground            | Ground return of the boost converter, buck switch ground                                               |

| 55            | BSTSW    | Output          | Boost Switch                      | Boost switch driver output to connect boost inductor                                                   |

| 56            | VER      | Input           | Energy Reserve Voltage            | Energy reserve voltage input for the storage capacitor charge control and energy reserve monitor       |

| 57            | WAKE     | Input           | Wake-up                           | Wake-up signal input to start-up boost and buck converters                                             |

| 58            | VPWR     | Input           | Power Supply                      | Battery voltage power supply input                                                                     |

| 59            | VSYNC    | Input/output    | Sensor Sync Power<br>Supply       | Satellite sensor sync voltage supply charge/discharge connection                                       |

| 60            | CPC2     | Output          | Charge Pump Capacitor<br>Pin2     | Charge pump capacitor pin2                                                                             |

| 61            | CPC1     | Output          | Charge Pump Capacitor<br>Pin1     | Charge pump capacitor pin1                                                                             |

| 62            | CPGND    | Ground          | Charge Pump Ground                | Charge pump ground                                                                                     |

| 63            | VBUCK_R  | Input           | Buck Converter<br>Redundant Input | Redundant buck converter input to supply current for charge pump                                       |

| 64            | VBUCK    | Input           | Buck Converter Input              | Buck converter input for buck loop feedback and current source of charge pump                          |

# **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

# Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                                                                                                                                               | Symbol                                                                                                            | Value       | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------|------|

| ELECTRICAL RATINGS                                                                                                                                                                                                                                    |                                                                                                                   |             | 1    |

| Supply Input Voltage                                                                                                                                                                                                                                  | $V_{PWR}$                                                                                                         | -0.3 to 40  | V    |

| Wake-up Input Voltage                                                                                                                                                                                                                                 | $V_{WAKE}$                                                                                                        | -16 to 40   | V    |

| Supply Voltage - 1                                                                                                                                                                                                                                    | V <sub>BST</sub> , V <sub>BSTSW</sub> , V <sub>BUCKSW</sub> , V <sub>ERSW</sub> , V <sub>ER</sub>                 | -0.3 to 40  | V    |

| Supply Voltage - 2                                                                                                                                                                                                                                    | V <sub>SYNC</sub> , V <sub>CPC2</sub>                                                                             | -0.3 to 20  | V    |

| Supply Voltage - 3                                                                                                                                                                                                                                    | V <sub>CPC1</sub> , V <sub>BUCK</sub> , V <sub>BUCK</sub> R, V <sub>CCDRI</sub>                                   | -0.3 to 10  | V    |

| Supply Voltage - 4                                                                                                                                                                                                                                    | V <sub>ERDIAG</sub>                                                                                               | -0.3 to 7   | V    |

| Supply Voltage - 5                                                                                                                                                                                                                                    | V <sub>CC</sub>                                                                                                   | -0.3 to 5.5 | V    |

| Supply Voltage - 6                                                                                                                                                                                                                                    | V <sub>DD</sub> , V <sub>BSTCOMP1</sub> , V <sub>BSTCOMP2</sub> , V <sub>BUCKCOMP1</sub> , V <sub>BUCKCOMP2</sub> | -0.3 to 3   | V    |

| LIN Interface Voltage                                                                                                                                                                                                                                 | $V_{LIN}$                                                                                                         | -27 to 40   | V    |

| I/O Voltage - 1                                                                                                                                                                                                                                       | V <sub>OUT1_D</sub> , V <sub>OUT1_S</sub> , V <sub>OUT2_D</sub> , V <sub>OUT2_S</sub>                             | -1 to 40    | V    |

| I/O Voltage - 2                                                                                                                                                                                                                                       | V <sub>IN1</sub> ~ V <sub>IN9</sub> , V <sub>PSI5_1</sub> ~ V <sub>PSI5_4</sub>                                   | -1 to 20    | V    |

| I/O Voltage - 3                                                                                                                                                                                                                                       | V <sub>ARM</sub> , V <sub>DISARM</sub> , V <sub>PPT</sub>                                                         | -0.3 to 10  | V    |

| I/O Voltage - 4                                                                                                                                                                                                                                       | Va sensor, Vaout, Vasst, Vscrap, Vreset, Vtxd, Vrxd, Vsi, Vso, Vsck, Vclk, Vcs, Vcsa, Vcsb, Vcsb, Vcsc, Vsatsync  | -0.3 to 5.5 | V    |

| GND Shift                                                                                                                                                                                                                                             | V <sub>SS</sub> , V <sub>GND_LIN</sub> , V <sub>CPGND</sub> , V <sub>GND_PSI</sub>                                | -0.3 to 0.3 | V    |

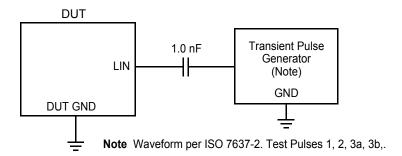

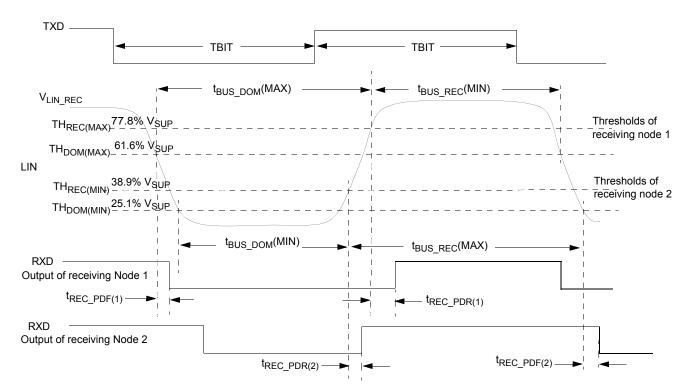

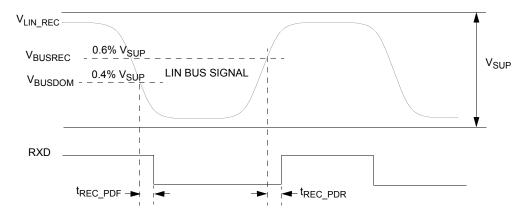

| LIN Bus Voltage <sup>(2)</sup> Normal Operation (DC) Transient (Coupled Through 1.0 nF Capacitor, according to ISO7637-2 & ISO7637-3) (See <u>Table 4</u> and <u>Figure 4</u> ) - Pulse 1 (test up to the limit for Damage - Class C <sup>(1)</sup> ) | V <sub>BUS(SS)</sub>                                                                                              | -27 to 40   | V    |

| - Pulse 2a (test up to the limit for Damage - Class $C^{(1)}$ )                                                                                                                                                                                       | V <sub>BUS(S1)</sub>                                                                                              | -100        |      |

| - Pulse 3a (test up to the limit for Damage - Class                                                                                                                                                                                                   | V <sub>BUS(S2A)</sub>                                                                                             | +75         |      |

| C <sup>(1)</sup> ) - Pulse 3b (test up to the limit for Damage - Class                                                                                                                                                                                | V <sub>BUS(S3A)</sub>                                                                                             | -150        |      |

| - Pulse 3b (test up to the limit for Damage - Class $C^{(1)}$ )                                                                                                                                                                                       | V <sub>BUS(S3B)</sub>                                                                                             | +100        |      |

### Notes

- 1. Class C: At least one function of the transceiver stops working properly during the test, and will return to the proper operation automatically when the exposure to the disturbance has ended. No physical damage of the IC occurs.

- 2. The LIN bus voltage is applied on the LIN pin as  $\rm V_{LIN}$  during tests.

#### Table 3. Maximum Ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                                                                                                                         | Symbol                                                                        | Value                      | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------|------|

| ESD Capability                                                                                                                                                                                                                  |                                                                               |                            |      |

| AECQ100                                                                                                                                                                                                                         |                                                                               |                            |      |

| Human Body Model - JESD22/A114 <sup>(3)</sup> All pins Charge Device Model - JESD22/C101 <sup>(3)</sup> Corner pins VCCDRI pin                                                                                                  | V <sub>ESD1-1</sub> V <sub>ESD2-1</sub> V <sub>ESD2-2</sub>                   | ±2.0 k<br>±750<br>±400     | V    |

| All other pins                                                                                                                                                                                                                  | V <sub>ESD2-3</sub>                                                           | ±500                       | •    |

| Additional for LIN Conformance  Contact Discharge, Unpowered <sup>(4)</sup> LIN pin without capacitor  LIN pin with 220 pF capacitor  LIN pin with 220 pF capacitor and indirect ESD coupling (according to ISO10605 - Annex F) | V <sub>LIN_ESD1-1</sub><br>V <sub>LIN_ESD1-2</sub><br>V <sub>LIN_ESD1-3</sub> | ±6.0 k<br>±6.0 k<br>±8.0 k |      |

| THERMAL RATINGS                                                                                                                                                                                                                 |                                                                               |                            |      |

| Operating Temperature Junction Temperature Case (Exposed Pad) Temperature                                                                                                                                                       | T <sub>J</sub><br>T <sub>C</sub>                                              | -40 to 150<br>-40 to 125   | °C   |

| Storage Temperature                                                                                                                                                                                                             | T <sub>STG</sub>                                                              | -65 to +150                | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(5)</sup> , (6)                                                                                                                                                              | T <sub>PPRT</sub>                                                             | Note 6                     | °C   |

| THERMAL RESISTANCE                                                                                                                                                                                                              |                                                                               | 1                          | _ L  |

| Junction to Ambient (Natural Convection)                                                                                                                                                                                        | $\theta_{JA}$                                                                 | 26                         | °C/W |

| Junction to Case (Exposed Pad)                                                                                                                                                                                                  | $\theta_{\sf JC}$                                                             | 1.5                        | °C/W |

#### Notes

- 3. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), and the Charge Device Model (CDM) ( $C_{ZAP}$  = 4.0 pF).

- According to "Hardware Requirements for LIN, CAN, and Flexray Interfaces in Automotive Applications" specification Rev. 1.1/December 2, 2009 (C<sub>ZAP</sub> = 150 pF, R<sub>ZAP</sub> = 330 Ω).

- 5. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 6. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts (i.e. MC33xxxD enter 33xxx), and review parametrics.

Table 4. Limits / Maximum Test Voltage for LIN Pin Transient Immunity Tests

| Test Pulse | V <sub>S</sub> [V] | Pulse Repetition<br>Frequency [Hz]<br>(1/T <sub>1</sub> ) | Test Duration [min] | R <sub>i</sub> [W] | Remarks             |

|------------|--------------------|-----------------------------------------------------------|---------------------|--------------------|---------------------|

| 1          | -100               | 2                                                         | 10                  | 10                 | t <sub>2</sub> = 0s |

| 2a         | +75                | 2                                                         | 10                  | 2                  |                     |

| 3а         | -150               | 10                                                        | 10                  | 50                 |                     |

| 3b         | +100               | 10                                                        | 10                  | 50                 |                     |

#### Notes

7. V<sub>SUP</sub> is applied on the VPWR pin as a test condition.

The I/V characteristic and leakage of the pin is performed before and after the test.

The supply pins and LIN must pass the  $V_S$  voltage level specified in <u>Table 4</u> without damage.

The failure validation during test is evaluated at RxD.

Tests perform in Normal mode on LIN (Failure on RxD), V<sub>SUP</sub> (Failure on LIN)<sup>(7)</sup>.

The voltage level found is for information only.

Failure criteria on RxD in Normal Mode:  $\pm 0.9$  V and  $\pm 7.5$   $\mu s$

Figure 4. Test Circuit for Transient Test Pulses (LIN)

# STATIC ELECTRICAL CHARACTERISTICS

# **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub><sup>(8)</sup>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Symbol                       | Characteristic                                                                                                                                            | Min                   | Тур                   | Max                   | Unit                | Notes |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|---------------------|-------|

| POWER MANAGE                 | MENT                                                                                                                                                      | I                     |                       |                       |                     |       |

| $V_{PWR}$                    | Power Supply Input Voltage<br>Normal Operation                                                                                                            | 5.2                   | -                     | 20                    | V                   |       |

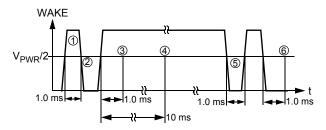

| V <sub>WAKE_TH</sub>         | Wake-up Threshold Voltage<br>Normal V <sub>PWR</sub> Range                                                                                                | 0.3* V <sub>PWR</sub> | 0.5* V <sub>PWR</sub> | 0.7* V <sub>PWR</sub> | V                   |       |

| R <sub>WAKE</sub>            | Wake-up Input Internal Pull-down Resistance                                                                                                               | 120                   | 200                   | 320                   | kΩ                  |       |

| V <sub>BST</sub>             | Boost Converter Output Voltage Normal $V_{PWR}$ Range, $0 \le I_{BST} \le Max$ . $I_{BST}$                                                                | 31.6                  | 33.3                  | 35                    | V                   |       |

| V <sub>BST_OV</sub>          | Boost Overvoltage Threshold                                                                                                                               | 36                    | 38                    | 40                    | V                   |       |

| V <sub>BST_OV_CLMP</sub>     | Boost Overvoltage Clamping Boost operating with active clamping                                                                                           | 40                    | 43                    | 46                    | V                   |       |

| V <sub>BST_OV_HYS</sub>      | Boost Overvoltage Hysteresis                                                                                                                              | 2.2                   | 2.6                   | 3.0                   | V                   |       |

| V <sub>BST_UV</sub>          | Low V <sub>PWR</sub> as Boost Undervoltage Lockout Threshold and IGNSTAT Detect Threshold                                                                 | 4.7                   | 4.95                  | 5.2                   | V                   |       |

| V <sub>BST_UV_HYS</sub>      | Boost Undervoltage Hysteresis                                                                                                                             | 0.3                   | 0.5                   | 0.8                   | V                   |       |

| R <sub>BSTSW_ON</sub>        | Boost Switch Transistor On Resistance                                                                                                                     | -                     | -                     | 550                   | mΩ                  |       |

| I <sub>BSTSW_LMT</sub>       | Boost Switch Current Limit                                                                                                                                | 1.3                   | 1.5                   | 1.8                   | А                   |       |

| T <sub>SW_SHDN</sub>         | Power Switch Thermal Shutdown                                                                                                                             | 155                   | 175                   | 195                   | °C                  |       |

| T <sub>SW_HYST</sub>         | Power Switch Thermal Shutdown Hysteresis                                                                                                                  | 15                    | -                     | 30                    | °C                  |       |

| ESR <sub>CERM</sub>          | Energy Reserve Capacitor ESR Measurement Range                                                                                                            | 200                   | -                     | 600                   | mΩ                  |       |

| -                            | C <sub>ER</sub> ESR Measurement Tolerance                                                                                                                 | -50                   | -                     | 50                    | mΩ                  |       |

| -                            | C <sub>ER</sub> Capacitance Measurement Tolerance                                                                                                         | -15                   | -                     | 15                    | %                   |       |

| R <sub>ERSW_CH_ON</sub>      | C <sub>ER</sub> Charge Transistor On Resistance                                                                                                           | 3.0                   | 10                    | 14                    | Ω                   |       |

| I <sub>ERSW_CH_SHDN</sub>    | C <sub>ER</sub> Charge Transistor Overcurrent Shutdown Threshold                                                                                          | 400                   | 550                   | 800                   | mA                  |       |

| R <sub>ERSW_DISCH_ON</sub>   | C <sub>ER</sub> Discharge Transistor On Resistance                                                                                                        | 2.0                   | 5.5                   | 8.0                   | Ω                   |       |

| I <sub>ERSW_DISCH_SHDN</sub> | C <sub>ER</sub> Discharge Transistor Overcurrent Shutdown Threshold                                                                                       | 350                   | 450                   | 800                   | mA                  |       |

| I <sub>ERSW_LEAK</sub>       | ERSW Pin Leakage Current                                                                                                                                  | -                     | -                     | 250                   | nA                  |       |

| I <sub>VER_LEAK</sub>        | VER Pin Leakage Current                                                                                                                                   | -                     | -                     | 200                   | μΑ                  |       |

| V <sub>ER_RESD</sub>         | C <sub>ER</sub> Residual Voltage after 10 s Discharge                                                                                                     | -                     | -                     | 2.5                   | V                   |       |

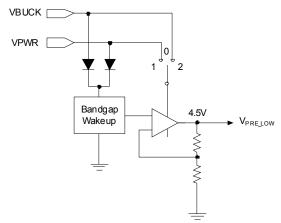

| V <sub>BUCK</sub>            | Buck Converter Output Voltage $10~V \leq V_{BST} \leq 40~V,~100~mA \leq I_{BUCK} \leq I_{BUCK\_C}$                                                        | 8.73                  | 9.0                   | 9.27                  | V                   |       |

| V <sub>BUCK_OV_SHDN</sub>    | Buck Converter Output Overvoltage Shutdown Threshold                                                                                                      | 9.6                   | 10                    | 10.8                  | V                   |       |

| V <sub>BUCK_UV</sub>         | Low V <sub>BST</sub> as Buck Converter Start-up Threshold                                                                                                 | 13.5                  | 15.5                  | 17.5                  | V                   |       |

| V <sub>BUCK_RIPL</sub>       | Buck Converter Output Ripple Voltage<br>$6.0 \text{ V} \le \text{V}_{PRW} \le 40 \text{ V}$ , $100 \text{ mA} \le \text{I}_{BUCK} \le \text{I}_{BUCK\_C}$ | -                     | -                     | 460                   | ${\sf mV}_{\sf PP}$ |       |

#### Notes

<sup>8.</sup>  $V_{SUP}$  is applied on the VPWR pin as a test condition.

| Symbol                       | Characteristic                                                                                                                                             | Min                   | Тур        | Max                  | Unit                | Notes |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|----------------------|---------------------|-------|

| POWER MANAGE                 | MENT (CONTINUED)                                                                                                                                           |                       |            | 1                    |                     | .1    |

| I <sub>BUCK_C</sub>          | Buck Converter Output Current Capability                                                                                                                   | 400                   | -          | -                    | mA                  |       |

| V <sub>BUCK_LOAD</sub>       | Buck Converter Load Regulation $I_{BUCK} = 100 \text{ mA}, \Delta I_{BUCK} = 100 \text{ mA}$ $I_{BUCK} = 300 \text{ mA}, \Delta I_{BUCK} = 100 \text{ mA}$ |                       | 5.0<br>4.0 | 8.0<br>6.0           | mV                  |       |

| I <sub>BUCKSW_HS_LMT</sub>   | Buck High-side Switch Current Limit                                                                                                                        | 500                   | 800        | 1100                 | mA                  |       |

| V <sub>SYNC</sub>            | Sync Supply Output Voltage $6.0 \text{ V} \leq \text{V}_{PRW} \leq 40 \text{ V}$                                                                           | 15                    | -          | 2x V <sub>BUCK</sub> | V                   |       |

| V <sub>SYNC_RIPL</sub>       | Sync Supply Output Ripple Voltage $6.0 \text{ V} \leq \text{V}_{PRW} \leq 40 \text{ V}$                                                                    | -                     | -          | 300                  | ${\sf mV}_{\sf PP}$ |       |

| I <sub>SYNC_C</sub>          | Sync Supply Output Current Capability                                                                                                                      | 20                    | -          | -                    | mA                  |       |

| I <sub>SYNC_OC</sub>         | Sync Switch Overcurrent Protection Limit                                                                                                                   | 65                    | -          | 150                  | mA                  |       |

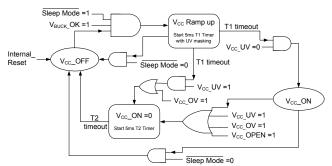

| V <sub>CC</sub>              | $V_{CC}$ Supply Output Voltage 6.0 V $\leq$ V <sub>BUCK</sub> $\leq$ 9.5 V, 0 $\leq$ I <sub>CC</sub> $\leq$ 200 mA                                         | 4.85                  | 5.0        | 5.15                 | V                   |       |

| -                            | $V_{CC}$ Supply Line Regulation $V_{PWR-AC}$ = 200 mV <sub>PP</sub> , $f_{PWR-AC} \le 500$ kHz                                                             | 20                    | -          | -                    | dB                  |       |

| -                            | $V_{CC}$ Supply Load Regulation $I_{CC-DC}$ = 0.8* $I_{CC\_MAX}$ , $\Delta I_{CC}$ = 50 mA                                                                 | -                     | -          | 10                   | mV                  |       |

| V <sub>CC_NOISE</sub>        | V <sub>CC</sub> Supply Noise Voltage                                                                                                                       | -                     | 5.0        | 20                   | $mV_{PP}$           |       |

| I <sub>VCCDRI_LMT</sub>      | V <sub>CC</sub> Base Driver Current Limit<br>T <sub>A</sub> = 25°C, Temperature coefficient = 300 ppm/ °C (typ.)                                           | 9.0                   | 13.5       | 22                   | mA                  |       |

| V <sub>BUCK_VCC</sub>        | Minimum V <sub>BUCK</sub> Voltage for V <sub>CC</sub> Operation                                                                                            | -                     | -          | 6.0                  | V                   |       |

| V <sub>BST_VCC</sub>         | Minimum V <sub>BST</sub> Voltage for V <sub>CC</sub> Operation                                                                                             | -                     | -          | 7.0                  | V                   |       |

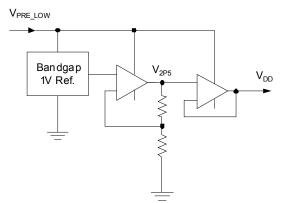

| $V_{DD}$                     | V <sub>DD</sub> Supply Voltage                                                                                                                             | -                     | 2.5        | -                    | V                   |       |

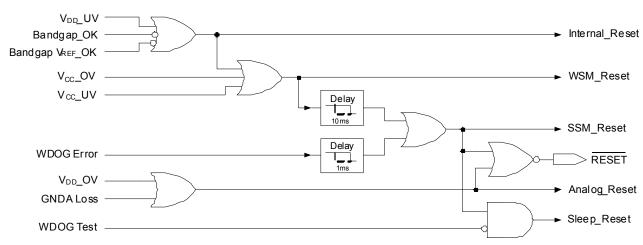

| RESET AND WAT                | CHDOG                                                                                                                                                      |                       |            | •                    |                     |       |

| V <sub>RESET_H</sub>         | Reset Output High IRESET = -2.0 mA                                                                                                                         | V <sub>CC</sub> - 0.4 | -          | V <sub>CC</sub>      | V                   |       |

| V <sub>RESET_L</sub>         | Reset Output Low IRESET = 2.0 mA                                                                                                                           | 0.0                   | -          | 0.4                  | V                   |       |

| V <sub>CC_OP</sub>           | Rising V <sub>CC</sub> Threshold for Reset Operation                                                                                                       | -                     | -          | 1.5                  | V                   |       |

| V <sub>CC_OV</sub>           | V <sub>CC</sub> Overvoltage for Reset                                                                                                                      | 5.2                   | -          | 5.5                  | V                   |       |

| V <sub>CC_UV</sub>           | V <sub>CC</sub> Undervoltage for Reset                                                                                                                     | 4.5                   | -          | 4.80                 | V                   |       |

| V <sub>CC_VM_HYS</sub>       | V <sub>CC</sub> Voltage Monitor Threshold Hysteresis                                                                                                       | 30                    | -          | -                    | mV                  |       |

| V <sub>DD_OV</sub>           | V <sub>DD</sub> Overvoltage for Reset                                                                                                                      | 2.7                   | -          | 3.0                  | V                   |       |

| V <sub>DD_UV</sub>           | V <sub>DD</sub> Undervoltage for Reset                                                                                                                     | 1.85                  | 1.90       | 2.10                 | V                   |       |

| V <sub>GNDA_GND_LIN_TH</sub> | GNDA to GND_LIN Voltage Difference to Activate Open GNDA Detection                                                                                         | 0.3                   | -          | 0.8                  | V                   |       |

| Symbol                       | Characteristic                                                                                                                                      | Min                        | Тур    | Max                        | Unit            | Notes |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------|----------------------------|-----------------|-------|

| SATELLITE SENSO              | OR INTERFACE                                                                                                                                        | 1                          |        |                            |                 | .1    |

| I <sub>SAT BUS</sub> SUP Q   | Satellite Bus Supply Quiescent Current                                                                                                              | -                          | -      | 2.2                        | mA              |       |

| I <sub>SAT_BUS_SUP</sub>     | Satellite Bus Supply Operation Current                                                                                                              | -                          | _      | 4.0                        | mA              |       |

| I <sub>SAT_SYNC_SUP_Q</sub>  | Sync Supply Quiescent Current                                                                                                                       | -                          | -      | 1.0                        | mA              |       |

| I <sub>SAT_SYNC_SUP</sub>    | Sync Supply Operation Current                                                                                                                       | -                          | -      | 1.0                        | mA              |       |

| I <sub>SAT_VCC_Q</sub>       | Satellite Logic Supply Quiescent Current                                                                                                            | -                          | -      | 1.0                        | mA              |       |

| I <sub>SAT_VCC</sub>         | Satellite Logic Supply Operation Current                                                                                                            | -                          | -      | 3.0                        | mA              |       |

| V <sub>SAT_OUT</sub>         | Satellite Interface DC Output Operation Voltage $0 \le I_{SAT\_OUT} \le 65 \text{ mA}$                                                              | 5.8                        | 6.3    | 6.7                        | V               |       |

| V <sub>SAT_OUT_DIS</sub>     | Satellite Interface DC Output Disable Voltage  I <sub>SAT_OUT</sub> = 0 mA                                                                          | -                          | -      | 0.5                        | V               |       |

| P <sub>SRRSAT_BUS_SUP</sub>  | Satellite Interface Ripple Rejection from Bus Supply 50 kHz $\leq$ f <sub>RIPL</sub> $\leq$ 280 kHz 280 kHz $\leq$ f <sub>RIPL</sub> $\leq$ 560 kHz | 30<br>20                   | -<br>- |                            | dB              |       |

| V <sub>SAT_RIPL</sub>        | Satellite Interface Ripple Voltage due to Current Modulation (typical application configuration)                                                    | -                          | -      | 200                        | ${\sf mV_{PP}}$ |       |

| V <sub>SAT_SYNC_ABS</sub>    | Sync Pulse Absolute Voltage                                                                                                                         | 10                         | -      | 12                         | >               |       |

| V <sub>SAT_SYNC_STEP</sub>   | Sync Pulse Voltage Step                                                                                                                             | V <sub>SAT_OUT</sub> + 4.3 | -      | V <sub>SAT_OUT</sub> + 5.5 | ٧               |       |

| V <sub>SATSYNC_L</sub>       | SATSYNC Input Low Voltage                                                                                                                           | -0.3                       | -      | 1.0                        | V               |       |

| V <sub>SATSYNC_H</sub>       | SATSYNC Input High Voltage                                                                                                                          | 2.0                        | -      | V <sub>CC</sub> +0.3       | V               |       |

| I <sub>SATSYNC_PULLDN</sub>  | SATSYNC Input Pull-down Current                                                                                                                     | 10                         | -      | 50                         | μΑ              |       |

| I <sub>SAT</sub>             | Satellite Interface Operational Current Range                                                                                                       | 0.0                        | -      | 65                         | mA              |       |

| I <sub>SAT_PD_LIM</sub>      | Satellite Interface Pull-down Current Limit                                                                                                         | 27                         | -      | 60                         | mA              |       |

| I <sub>SAT_OC</sub>          | Satellite Interface Overcurrent Limit                                                                                                               | 70                         | -      | 120                        | mA              |       |

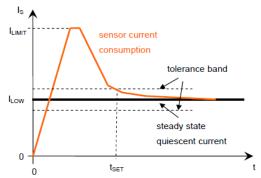

| I <sub>SAT_Q_RANGE_MIN</sub> | Minimum Satellite Quiescent Current Adaptation Level                                                                                                | 1.9                        | -      | 3.8                        | mA              |       |

| I <sub>SAT_Q_RANGE_MAX</sub> | Maximum Satellite Quiescent Current Adaptation Level                                                                                                | 35                         | -      | 50                         | mA              |       |

| I <sub>SAT_Q_</sub> SINGLE   | Satellite Quiescent Current for Single Satellite<br>Synchronous Satsync-steered Mode                                                                | 4.0                        | -      | 18.5                       | mA              |       |

| I <sub>SAT_Q_DUAL</sub>      | Satellite Quiescent Current for Dual Satellite<br>Synchronous Satsync-steered Mode                                                                  | 8.0                        | -      | 26.5                       | mA              |       |

| I <sub>SAT_Q_TOTAL</sub>     | Total Bus Quiescent Current<br>Synchronous TDM Mode                                                                                                 | 4.0                        | -      | 35                         | mA              |       |

| -                            | Satellite Quiescent Current Detect Accuracy 4.0 mA = Current Threshold = 14 mA 14 mA = Current Threshold = 35 mA                                    | -10<br>-6.0                | -      | 10<br>6.0                  | %               |       |

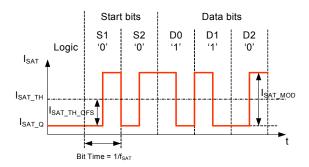

| I <sub>SAT_MOD</sub>         | Satellite Sensor Modulation Current                                                                                                                 | 20                         | -      | 30                         | mA              |       |

| I <sub>SAT_TH_RANGE</sub>    | Satellite Data Comparator Current Threshold Range                                                                                                   | 15.75                      | -      | 48.25                      | mA              |       |

| I <sub>SAT_TH_OFS</sub>      | Satellite Data Comparator Threshold Current Offset                                                                                                  | 11.25                      | 12.5   | 13.75                      | mA              |       |

| I <sub>SAT_TH_HYST</sub>     | Satellite Data Detection Current Threshold Hysteresis                                                                                               | 2.0                        | -      | 3.5                        | mA              |       |

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub><sup>(8)</sup>  $\leq$  18 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Symbol                     | Characteristic                                                                                                                                       | Min               | Тур            | Max            | Unit                 | Notes |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|----------------|----------------------|-------|

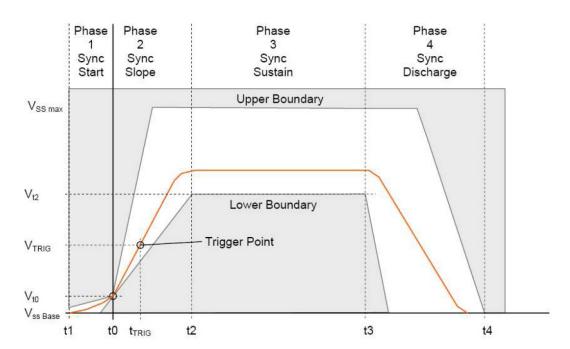

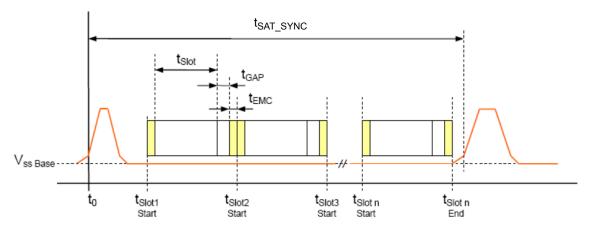

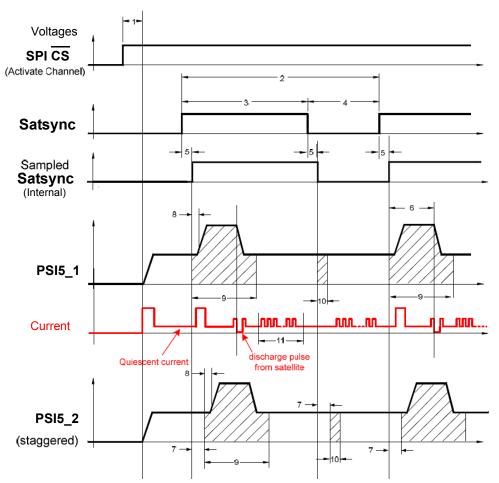

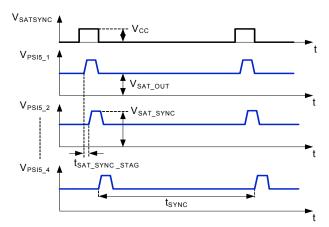

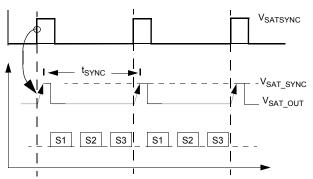

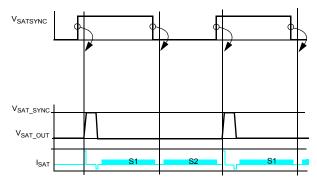

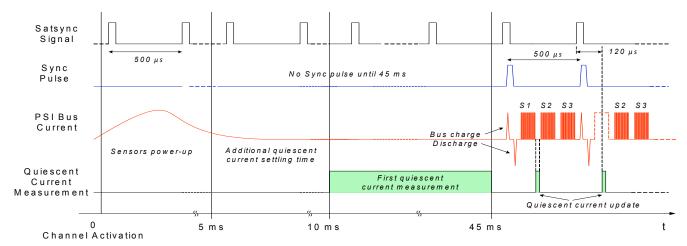

| SYNC PULSE LIM             | ITS FOR SYNCHRONOUS TDM MODE (SEE <u>Figure 5</u> . SYNCHRONO                                                                                        | OUS TOM MO        | DE SYNC PU     | JLSE TIMIN     | G)                   |       |

| $V_{t0}$                   | Sync Slope Reference Voltage                                                                                                                         | -                 | 0.5            | -              | V                    |       |

| V <sub>t2</sub>            | Sync Signal Sustain Voltage                                                                                                                          | 4.3               | -              | 5.5            | V                    |       |

| DC SENSOR INTE             | RFACE                                                                                                                                                | •                 |                |                |                      |       |

| I <sub>DCREG_LMT</sub>     | DC Sensor Supply Regulator Current Limit                                                                                                             | 30                | -              | 55             | mA                   |       |

| I <sub>DCREG_OC_DIFF</sub> | Current Difference Between the Regulator Overcurrent Detection Threshold and the Regulator Current Limit    DCREG_OC_DIFF =   DCREG_LMT -   DCREG_OC | 1.0               | 9.0            | 18             | mA                   | (9)   |

| V <sub>1</sub>             | Regulated Output Voltage 1                                                                                                                           | 1.35              | 1.5            | 1.73           | V                    |       |

| V <sub>2</sub>             | Regulated Output Voltage 2                                                                                                                           | 2.25              | 2.5            | 2.75           | V                    |       |

| V <sub>3</sub>             | Regulated Output Voltage 3                                                                                                                           | 4.5               | 5.0            | 5.5            | V                    |       |

| $V_4$                      | Regulated Output Voltage 4                                                                                                                           | 5.85              | 6.5            | 7.15           | V                    |       |

| -                          | Output Voltage Overshoot When Changing the Setting<br>Measured as Percentage of the Voltage Step                                                     | -                 | -              | 25             | %                    |       |

| R <sub>DCREG_FBK</sub>     | Regulator Feedback Load Resistance                                                                                                                   | 100               | 200            | 300            | kΩ                   |       |

| Th <sub>DCREG_SD</sub>     | Regulator Thermal Shutdown Temperature                                                                                                               | 155               | 175            | 195            | °C                   |       |

| Th <sub>DCREG_HYS</sub>    | Regulator Thermal Shutdown Hysteresis                                                                                                                | 15                | -              | 30             | °C                   |       |

| C <sub>INx</sub>           | INx Load Capacitance                                                                                                                                 | 12.5              | -              | 220            | nF                   |       |

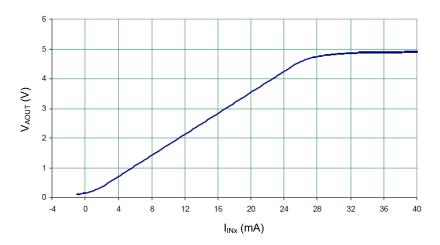

| K <sub>CONV</sub>          | DC Sensor Interface Current to Voltage Conversion Factor (See Figure 21)  I <sub>INx</sub> : 2.5 mA ~ 25 mA                                          | 0.163             | 0.177          | 0.190          | V/mA                 |       |

| V <sub>CONV_NLIN</sub>     | DC Sensor Interface Current to Voltage Conversion Nonlinearity                                                                                       | -                 | -              | 20             | ${\rm mV}_{\rm RMS}$ |       |

| V <sub>INX_I_</sub> OFS    | Current Measurement Output Offset Voltage $I_{INx}=0,\ C_{INx}=0.22\ nF,\ R_{INx}=1.0\ M\Omega$ $V_1=1.5\ V$ $V_2=2.5\ V$ $V_3=5.0\ V$               | 0.0<br>0.0<br>0.0 | 28<br>29<br>33 | 50<br>55<br>60 | mV                   |       |

# Notes

$V_{\mathsf{INx\_OFS}}$

I<sub>INx\_PULLDN</sub>

0.0

-110

38

-85

65

1.0

-30

٧

μΑ

$V_4 = 6.5 V$

INx Pin Offset Voltage

INx Active Pull-down Current

Voltage Source not Enable and  $I_{INx} = 0$

$2.0~V \leq V_{INx} \leq 7.15~V$  and INx is not selected

<sup>9.</sup> IDCREG\_OC is the regulator overcurrent detection threshold to trigger the regulator switch between a voltage source and a current source.

| Symbol                | Characteristic                                                                                     | Min          | Тур        | Max             | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------------------------------|--------------|------------|-----------------|------|-------|

| LOG OUTPL             | JT                                                                                                 | <u> </u>     | l .        | 1               |      |       |

| V <sub>AOUT</sub>     | Analog Output Voltage                                                                              | GND          | -          | V <sub>CC</sub> | V    |       |

| V <sub>AOUT_OFS</sub> | Analog Buffer Offset                                                                               | -20          | -          | 20              | mV   |       |

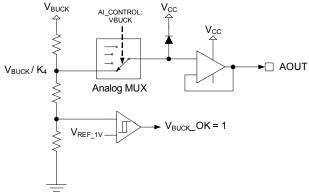

| А                     | Analog Output Buffer Gain For Output Voltage Monitors For DC Sensor Interface INx Voltage Monitors | 0.99<br>0.48 | 1.0<br>0.5 | 1.01<br>0.52    |      |       |

| K <sub>1</sub>        | Scale Factor of Pin VBST Monitor $V_{BST} \le 35 \text{ V}$                                        | 8.0          | 8.5        | 9.1             |      |       |

| K <sub>2</sub>        | Scale Factor of Pin VER Monitor $V_{ER} \le 35 \text{ V}$                                          | 8.0          | 8.5        | 9.1             |      |       |

| K <sub>3</sub>        | Scale Factor of Pin VERDIAG Monitor                                                                | 4.5          | 5.0        | 5.5             |      |       |

| K <sub>4</sub>        | Scale Factor of Pin VBUCK Monitor  V <sub>BUCK</sub> ≤ 10 V                                        | 2.6          | 2.8        | 2.9             |      |       |

| K <sub>5</sub>        | Scale Factor of Pin VSYNC Monitor V <sub>SYNC</sub> ≤ 20 V                                         | 4.5          | 5.0        | 5.5             |      |       |

| K <sub>6</sub>        | Scale Factor of Pin VPWR Monitor $V_{PWR} \le 20 \text{ V}$                                        | 5.2          | 5.6        | 5.9             |      |       |

| K <sub>7</sub>        | Scale Factor of Pin OUTx_D Monitor                                                                 | 5.2          | 5.6        | 5.9             |      |       |

| K <sub>8</sub>        | Scale Factor of Pin OUTx_S Monitor                                                                 | 5.2          | 5.6        | 5.9             |      | 1     |

| V <sub>OUTx_S_ON_HS</sub>     | Drain-Source On Voltage in High-side Driver Configuration $V_{OUTx_D}$ = 18 V, $I_{OUTx_S}$ = 70 mA                                                                                                                                               | V <sub>OUTx_D</sub><br>- 0.5 | -      | V <sub>OUTx_D</sub>          | V  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------|------------------------------|----|--|

| V <sub>OUTx_D_ON_LS</sub>     | Drain-Source On Voltage in Low-side Driver Configuration $V_{OUTx\_S} = 0 \text{ V}, I_{OUTx\_D} = 70 \text{ mA}$                                                                                                                                 | V <sub>OUTx_S</sub>          | -      | V <sub>OUTx_S</sub><br>+ 0.5 | ٧  |  |

| I <sub>OUTx_S_LMT</sub>       | High-side Driver Current Limit $V_{OUTx\_D} = 18 \text{ V}, V_{OUTx\_S} = 0 \text{ V}$                                                                                                                                                            | 70                           | -      | 110                          | mA |  |

| I <sub>OUTx_D_LMT</sub>       | Low-side Driver Current Limit  V <sub>OUTx_D</sub> = 18 V, V <sub>OUTx_S</sub> = 0 V                                                                                                                                                              | -110                         | -      | -70                          | mA |  |

| Th <sub>OUTx_SD</sub>         | Driver Thermal Shutdown Temperature                                                                                                                                                                                                               | 155                          | 175    | 195                          | °C |  |

| Th <sub>OUTx_HYS</sub>        | Driver Thermal Shutdown Hysteresis                                                                                                                                                                                                                | 15                           | -      | 30                           | °C |  |

| I <sub>OUTx_D_LEAK_GND</sub>  | Drain Leakage to GND  VRESET = 0 V, or in Sleep Mode, VOUTX_D = 0 V  VRESET = 5 V, VPWR = 18 V, Driver Off, VOUTX_D = 0 V                                                                                                                         | -1.0<br>45                   | -<br>- | 1.0<br>100                   | μА |  |

| IOUTx_D_LEAK_BAT              | Drain Leakage to Battery  VRESET = 0 V, V <sub>OUTx_D</sub> = V <sub>PWR</sub> VRESET = 5.0 V, V <sub>PWR</sub> = 18 V, Driver Off, V <sub>OUTx_D</sub> = 18 V                                                                                    | -1.0<br>-100                 | -      | 1.0<br>-45                   | μА |  |

| V <sub>OUTx_D_OPEN</sub>      | Open Drain Voltage VRESET = 5.0 V, Driver Off                                                                                                                                                                                                     | 0.4 x V <sub>PWR</sub>       | -      | 0.6 x V <sub>PWR</sub>       | ٧  |  |

| I <sub>OUTx_</sub> S_LEAK_GND | Source Leakage to GND $V_{\overline{RESET}} = 0 \text{ V, or in Sleep Mode, } V_{\overline{OUTx\_S}} = 0 \text{ V}$ $V_{\overline{RESET}} = 5.0 \text{ V, } V_{\overline{PWR}} = 18 \text{ V, Driver Off, } V_{\overline{OUTx\_S}} = 0 \text{ V}$ | -1.0<br>50                   | -      | 1.0<br>100                   | μА |  |

| Symbol                       | Characteristic                                                                                                                                | Min                         | Тур                         | Max                         | Unit | Notes |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|------|-------|

| CONFIGURABLE I               | DRIVERS (CONTINUED)                                                                                                                           |                             |                             | I                           |      |       |

| I <sub>OUTx_S_LEAK_BAT</sub> | Source Leakage to Battery  VRESET = 0 V, VOUTX_S = VPWR  VRESET = 5.0 V, VPWR = 18 V, Driver Off, VOUTX_S = 18 V                              | 0.0<br>-100                 | -<br>-                      | 300<br>-50                  | μΑ   |       |

| V <sub>OUTx_S_OPEN</sub>     | Open Source Voltage VRESET = 5.0 V, Driver Off                                                                                                | 0.4 x V <sub>PWR</sub>      | -                           | 0.6 x V <sub>PWR</sub>      | V    |       |

| V <sub>TH_2/3</sub>          | 2/3 $V_{PWR}$ Comparator Threshold for Diagnostics 6.0 $V \le V_{PWR} \le$ 18 $V$                                                             | 0.6 x V <sub>PWR</sub>      | 0.666 x<br>V <sub>PWR</sub> | 0.734 x<br>V <sub>PWR</sub> | V    |       |

| V <sub>TH_1/3</sub>          | 1/3 $V_{PWR}$ Comparator Threshold for Diagnostics 6.0 $V \le V_{PWR} \le 18 V$                                                               | 0.266 x<br>V <sub>PWR</sub> | 0.333 x<br>V <sub>PWR</sub> | 0.4 x V <sub>PWR</sub>      | V    |       |

| D <sub>OUTx</sub>            | PWM Duty Cycle Fixed Frequency = 128 Hz, Increment step = 1.6%                                                                                | 0.0                         | -                           | 100                         | %    |       |

| GENERAL LOGIC                | INPUTS: CS, CS_X, SCK, SI, ASST, SCRAP, CLK                                                                                                   | 1                           |                             | 1                           |      |       |

| V <sub>LGIN_H</sub>          | Logic Input High                                                                                                                              | 2.0                         | -                           | V <sub>CC</sub> + 0.3       | V    |       |

| $V_{LGIN_{L}}$               | Logic Input Low                                                                                                                               | -0.3                        | -                           | 1.0                         | V    |       |

| I <sub>LGIN_PULLUP</sub>     | Logic Input Pull-up Current For $\overline{CS}$ : $V_{LGIN}$ = $V_{\overline{CS}} \le 2.0 \text{ V}$ For others: $V_{LGIN} \le 4.5 \text{ V}$ | 10                          | -                           | 50                          | μА   |       |

| I <sub>LGIN_</sub> LEAK      | Logic Input Leakage V <sub>LGIN</sub> = V <sub>DD</sub>                                                                                       | -2.0                        | -                           | 5.0                         | μA   |       |

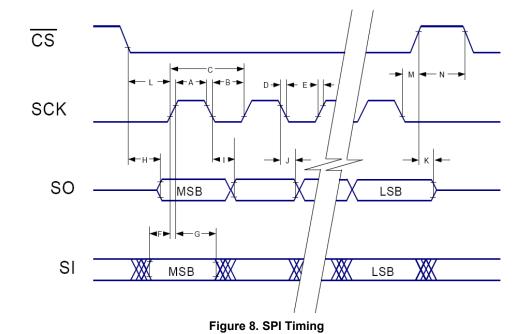

| SPI (OTHERS) AN              | D SPI MONITOR INTERFACE                                                                                                                       |                             |                             | l l                         |      | _1    |

| V <sub>SO_L</sub>            | SO Voltage Low<br>I <sub>SO</sub> = 0.5 mA                                                                                                    | -                           | -                           | 0.4                         | V    |       |

| V <sub>SO_H</sub>            | SO Voltage High I <sub>SO</sub> = -0.2 mA                                                                                                     | V <sub>CC</sub> - 0.4       | -                           | V <sub>CC</sub>             | V    |       |

| ANALOG SENSOF                | RINPUT                                                                                                                                        |                             |                             | I                           |      |       |

| V <sub>IN_ANA</sub>          | Analog Sensor Input Voltage                                                                                                                   | 0.0                         | -                           | $V_{CC}$                    | V    |       |

| I <sub>IN_ANA</sub>          | Analog Sensor Input Pull-down Current                                                                                                         | 2.0                         | -                           | 8.0                         | μA   |       |

| ARM ENABLE / DI              | SABLE OUTPUTS                                                                                                                                 | •                           |                             | <u>'</u>                    |      | •     |